面试

MCU

qt

动态规划

visual studio

慢速外设接口

binder

深度遍历

笔记

LAMBDA

《红宝石》

绘图机器人

matlab入门案例

智能家居

decodeByteArray

python考级

gerapy

macos

心理健康管理系统

二分

VIVADO

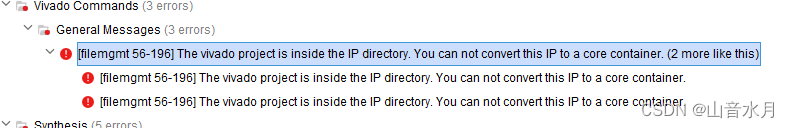

2024/4/11 17:23:33Vivado [filemgmt 56-328]生成ip报错解决方法

报错为:[filemgmt 56-328] 在block design子模块中加入新的Ip,就会进行这样的报错。 原因:生成ip时选错选项 解决方法:在配置完ip后点ok,弹出Generate OutPut Products窗口,不要直接点Generate,…

【Vivado那些事儿】多版本VIVADO,怎么设置默认运行版本?

多版本VIVADO,怎么设置默认运行版本?前言问题解决结语前言

有过工程开发经验的小伙伴都会有过在同一台计算机上安装多个Vivado版本的情况,例如装了Vivado 2018.3、Vivado 2018.2、Vivado 2021.1这三个版本。当在开发FPGA项目时,会…

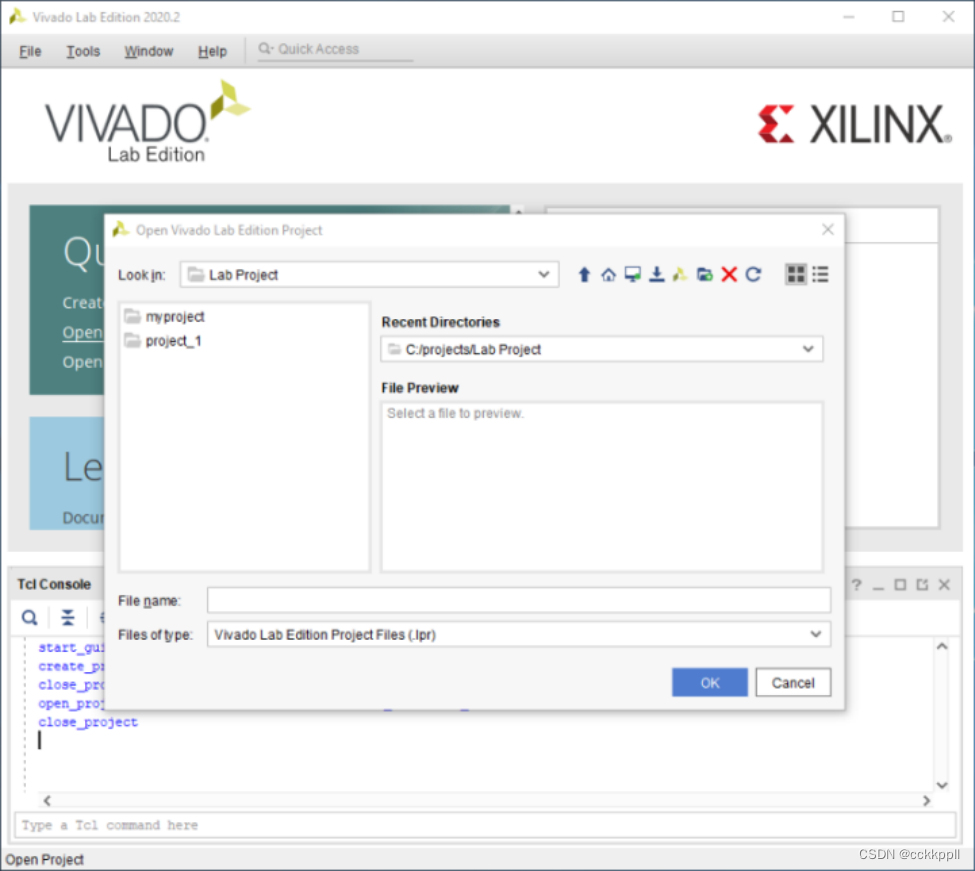

Vivado Lab Edition

Vivado Lab Edition 是完整版 Vivado Design Suite 的独立安装版本 , 包含在生成比特流后对赛灵思 FPGA 进行编程和 调试所需的所有功能。通常适用于在如下实验室环境内进行编程和调试: 实验室环境中的机器所含磁盘空间、内存和连 接资源较少。Vivad…

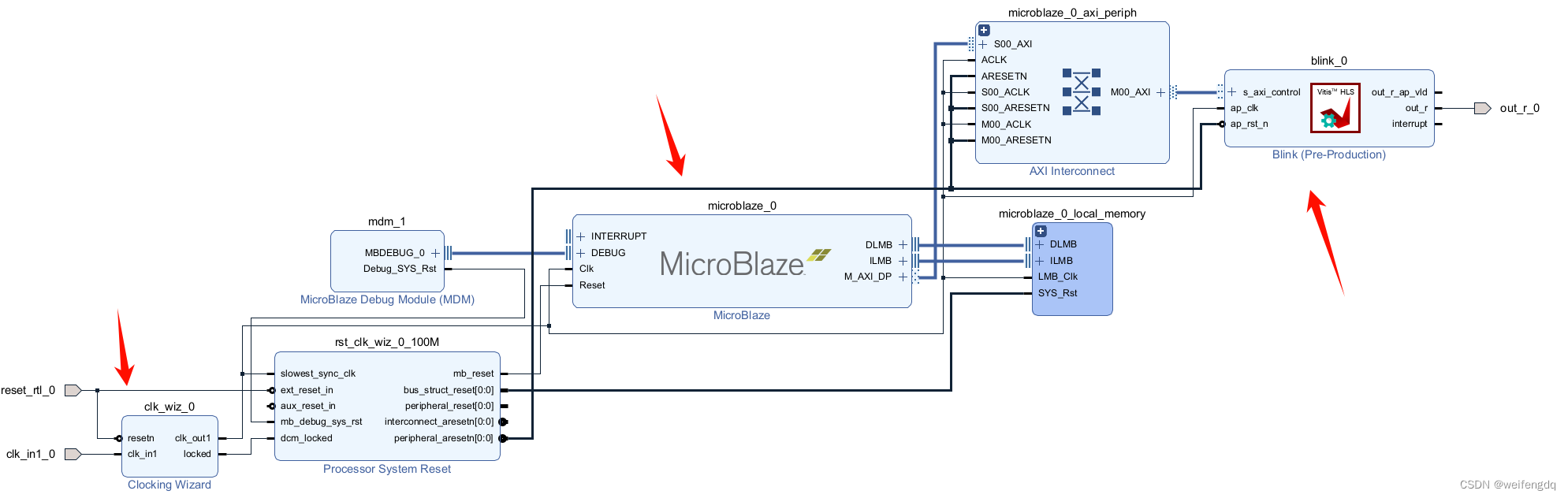

ZYNQ之嵌入式学习----开篇实验Hello World

1 ZYNQ 嵌入式系统的开篇实验Hello World

阅读本文需先学习: FPGA学习----Vivado软件使用

1.1 ZYNQ 嵌入式系统开发流程

创建Vivado工程使用IP Integrator 创建 Processor System生成顶层HDL生成比特流,导出到SDK在SDK中创建应用工程板级验证

开篇实验任务是在 …

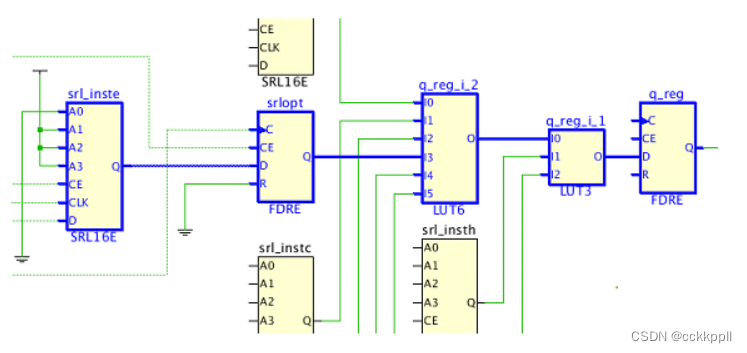

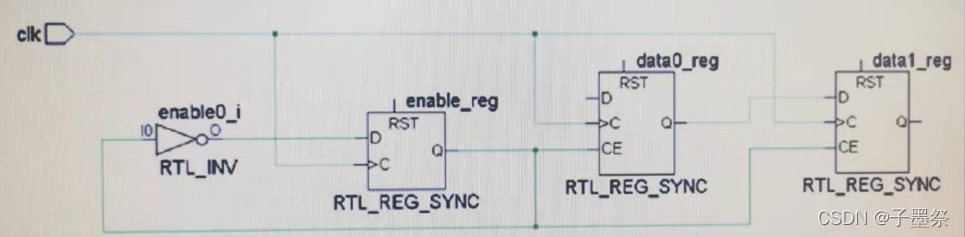

vivado中移位寄存器的优化(二)

移位寄存器优化用于改善移位寄存器单元(SRLs)与其他逻辑单元之间的负裕量路径的时序。如果存在对移位寄存器单元(SRL16E或SRLC32E)的时序违规,优化会从SRL寄存器链的开始或结束位置提取一个寄存器,并将其放…

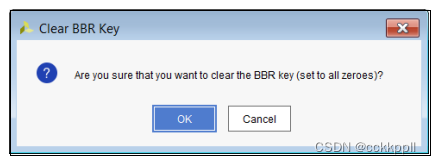

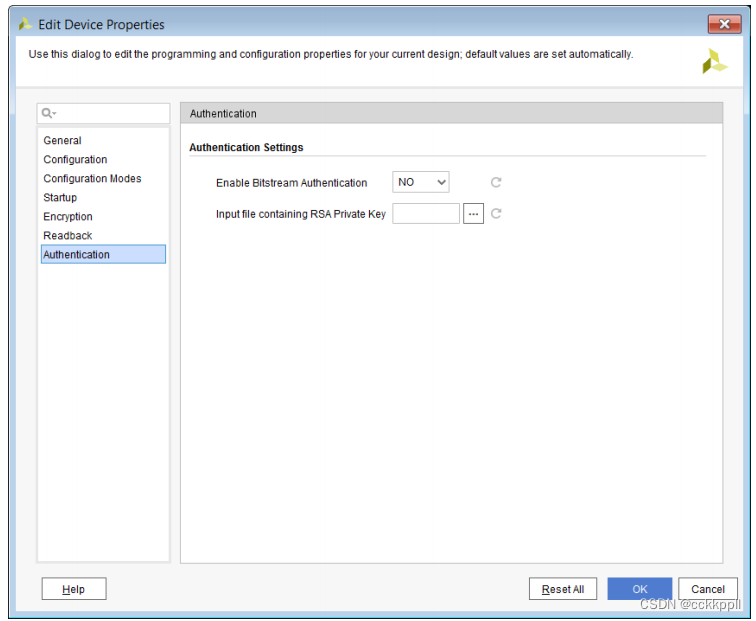

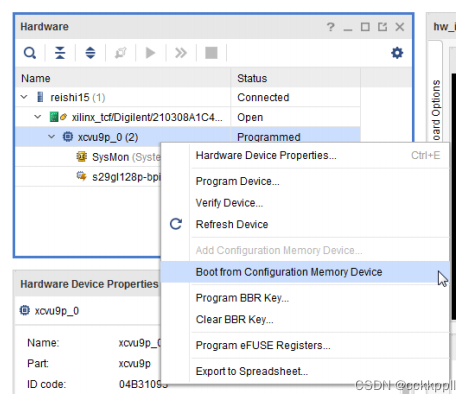

vivado 面向 7 系列器件的 AES 密钥编程

要将 AES 密钥编程到 BBR 中 , 请在“硬件 (Hardware) ”窗口中右键单击 FPGA 器件并选中“ Program BBR Key ”。 在“ BBR 密钥编程 (Program BBR Key) ”对话框中 , 输入文件名或者浏览至目标文件以指定 AES 密钥文件 ( .nky ) 。指 定有效的 .n…

Vivado 设计实现时报错The design is empty的解决方案(亲测有效)

[Place 30-494] The design is empty

使用Vivado进行设计实现时,点击Run Implementation,运行过程报错The design is empty,如图所示: 报错原因

因为设计只有输入,synthesis tool 可以优化到什么都没有。换句话说&am…

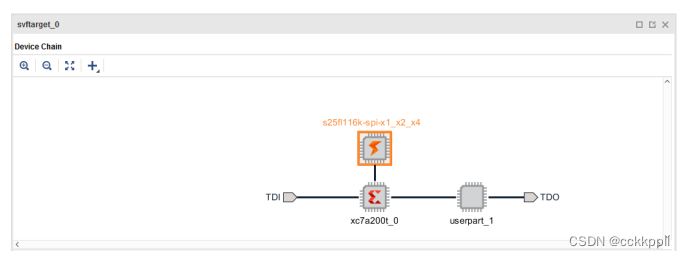

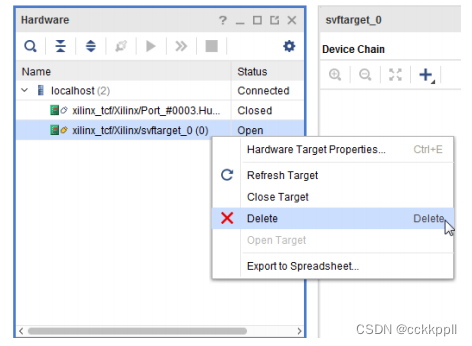

vivado向赛灵思器件添加配置存储器器件

使用 Vivado IDE 右键单击 SVF 链中的赛灵思器件时 , 可以选择创建配置存储器器件 , 并将配置存储器器件与该器件关联。 这样会打开“添加配置存储器器件 (Add Configuration Memory Device) ”对话框 , 如下所示。 选择相应的存储器器件…

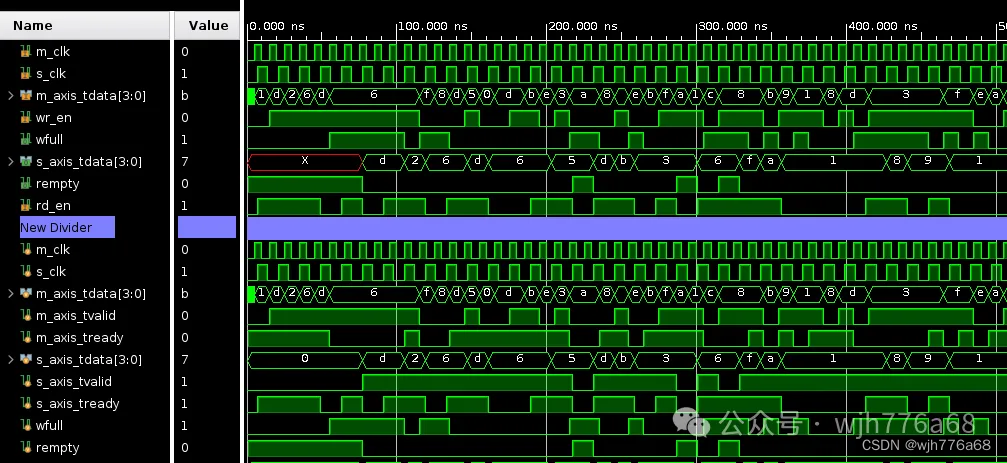

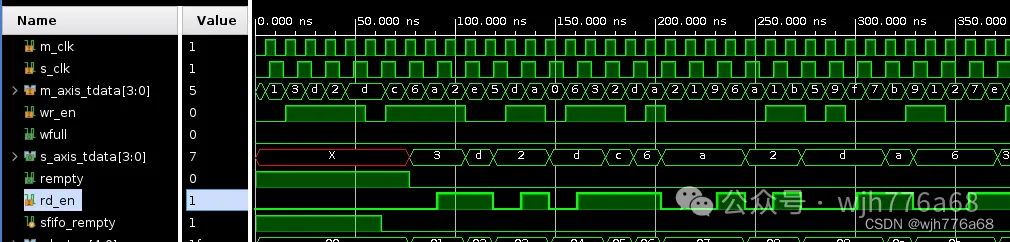

【AXIS】AXI-Stream FIFO设计实现(四)——异步时钟

前文介绍了几种同步时钟情况下的AXI Stream FIFO实现方式,一般来说,FIFO也需要承担异步时钟域模块间数据传输的功能,本文介绍异步AXIS FIFO的实现方式。 如前文所说,AXI-Stream FIFO十分类似于FWFT异步FIFO,推荐参考前…

在 Vivado 中执行远程调试

在 Vivado 中执行远程调试 远程调试需求可能在各种情况下出现。在产品原型设计阶段可能需要远程调试以便您在无法实地访问实验室的情况下对 实验室中的设计进行调试, 或者供您在组织内部共享资源。执行现场调试以诊断问题或者延长产品生命周期时也可能需 要远程调…

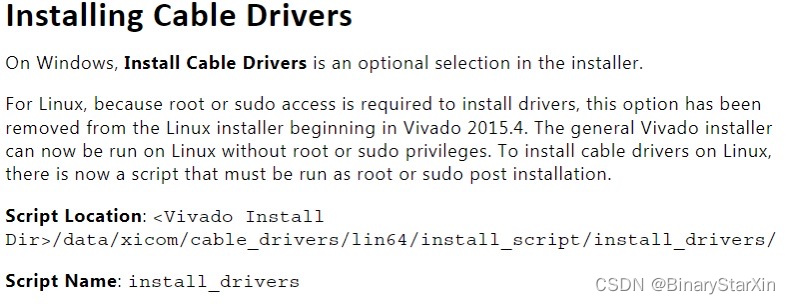

2、Ubuntu下安装Vivado下的下载器驱动 Digilent 版本

简介

在Ubuntu下安装Vivado时,安装工具会提醒你,digilent驱动无法自动安装,需要手动安装,并且让用户参考UG973手册安装。

由于安装驱动很简单,不用麻烦大家去找手册了,这里直接给出安装方法

安装方法

…

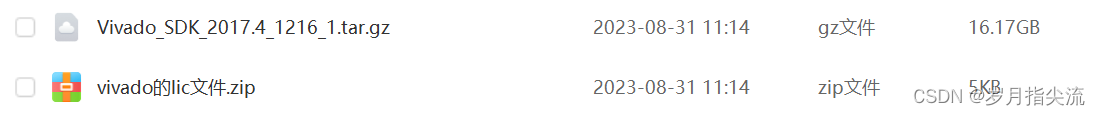

Vivado 2017.04版本安装教程

文章目录 前言一、vivado 简介二、vivado 下载三、vivado 安装四、vivado 申请证书五、关闭升级提醒六、资源自取 前言

本文记录了在 windows 11 下安装 vivado 2017 的详细步骤。 一、vivado 简介

Vivado 是 Xilinx 公司于 2012 推出的新一代集成设计环境,虽然目…

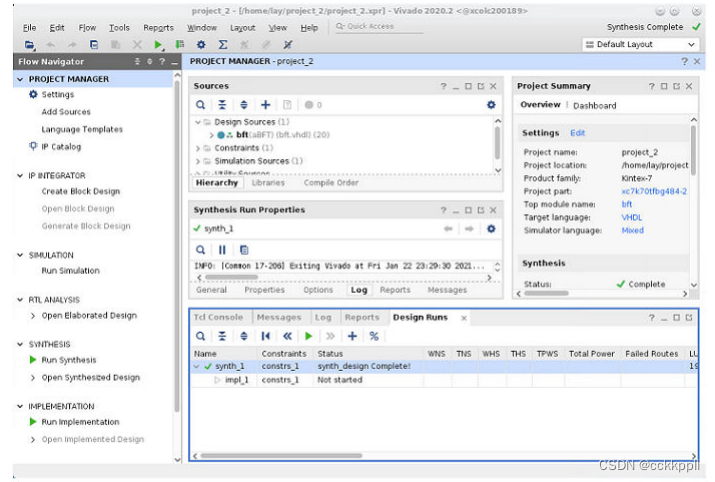

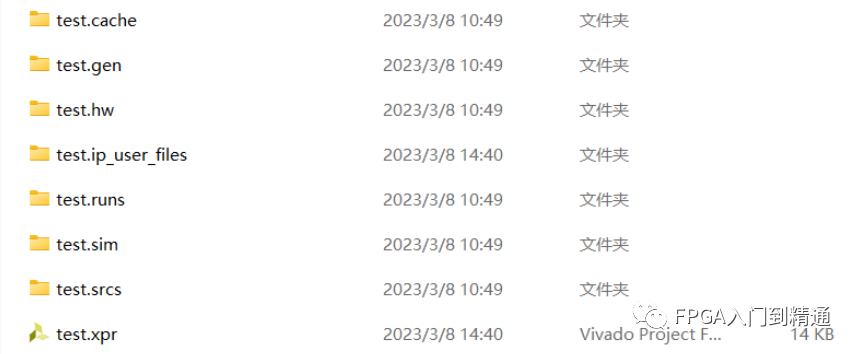

ZYNQ之FPGA学习----Vivado软件使用

1 Vivado软件使用

Vivado Design Suite 是 Xilinx 公司的综合性 FPGA 开发软件,可以完成从设计输入到硬件配置的完整FPGA 设计流程。Vivado学习使用版本为Vivado v18.3

Vivado软件使用流程:

新建工程设计输入分析与综合约束输入设计实现生成和下载比特…

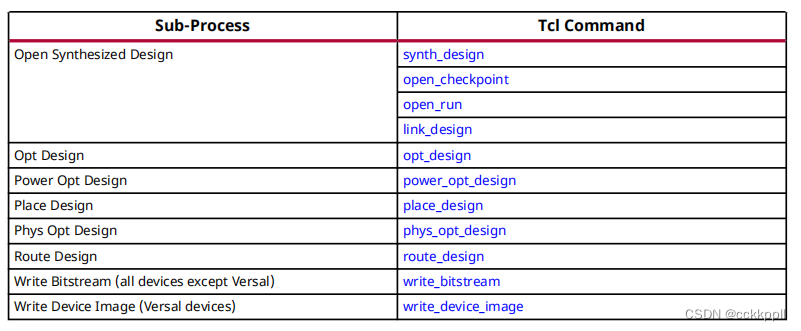

vivado 物理优化

物理优化

物理优化对的负松弛路径执行定时驱动优化设计物理优化有两种操作模式:后地点和后路线。在后置模式中,优化是基于基于单元放置的时序估计进行的。

由于逻辑优化和根据需要放置单元格。在路由后模式中,优化是基于实际的路由延迟进行…

FPGA 学习笔记:Vivado 工程管理技巧

前言 当前使用 Xilinx 的 FPGA,所以需要熟悉 Xilinx FPGA 的 开发利器 Vivado 的工程管理方法 这里初步列举一些实际 Xilinx FPGA 开发基于 Vivado 的项目使用到的工程的管理技巧 代码管理 做过嵌入式软件或者其他软件开发的工程技术人员,都会想到使用代码管理工具,如 SVN 、…

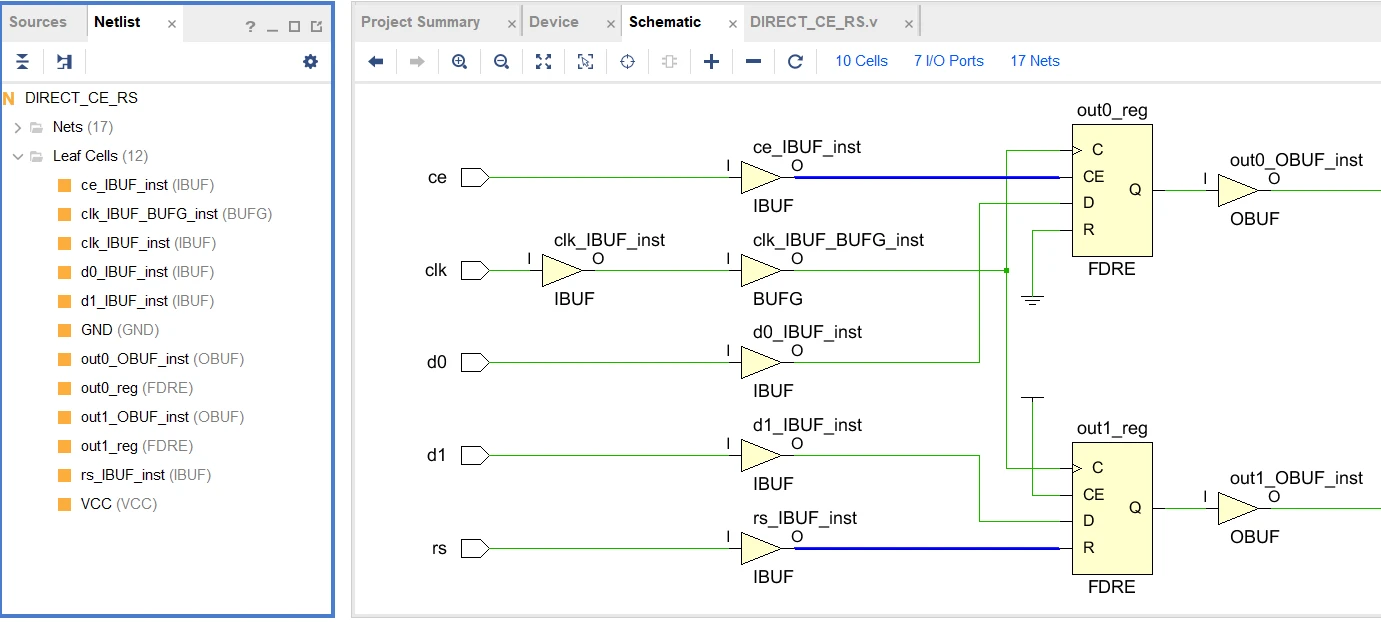

Vivado综合属性系列之八 DIRECT_ENABLE DIRECT_RESET

目录

一、前言

二、DIRECT_ENABLE、DIRECT_RESET 2.1 属性说明 2.2 工程代码 2.3 综合结果 一、前言 在Vivado 2019之前的版本中,对于设计中触发器的使能端口和复位端口是会自动接地,如果需要接设计端口,如果要直连…

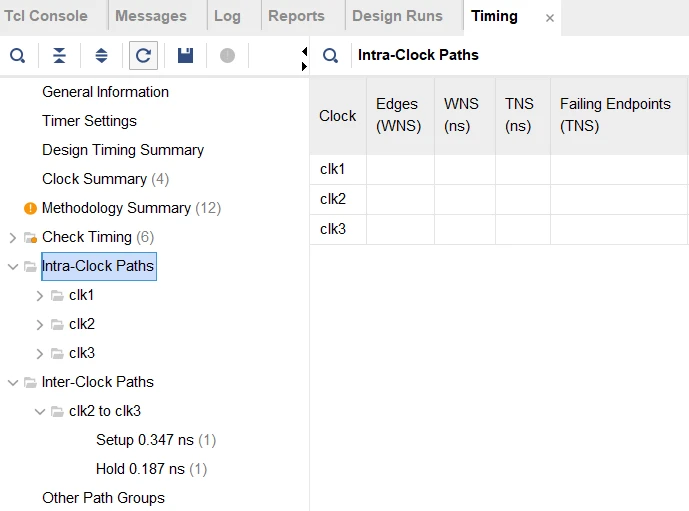

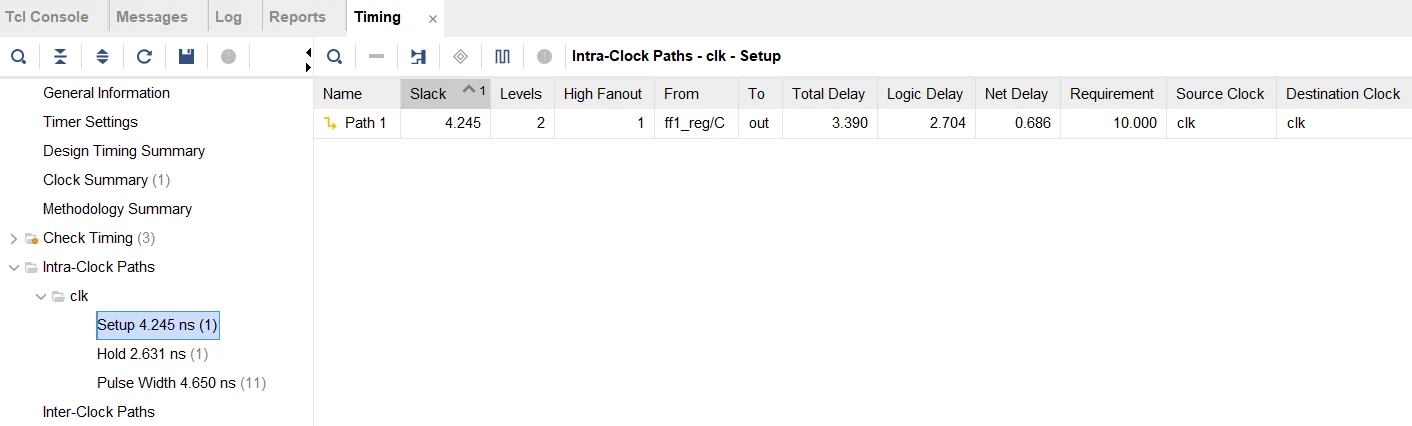

FPGA时序约束系列文章汇总

时序约束在FPGA开发中起着非常关键的作用。

与时序约束相关的方面包括时钟分析、路径分析、布线和布局优化等。时序约束的正确性和准确性对于设计的成功是至关重要的,因为它们对电路的时序性能、功耗和资源利用率有着重要影响。

有效的时序约束可以帮助设计人员充…

FPGA时序约束--实战篇(时序收敛优化)

目录

一、模块运行时钟频率

二、HDL代码

1、HDL代码风格

2、HDL代码逻辑优化

三、组合逻辑层数

1、插入寄存器

2、逻辑展平设计

3、防止变量被优化

四、高扇出

1、使用max_fanout

2、复位信号高扇出

五、资源消耗

1、优化代码逻辑,减少资源消耗。

2、…

vivado 布线、路线_设计

路由

Vivado路由器对放置的设计执行路由,并对路由设计,以解决保留时间冲突。Vivado路由器从放置的设计开始,并尝试路由所有网络。它可以从已放置的未布线、部分布线或完全布线的设计。对于部分路由的设计,Vivado路由器使用现有的…

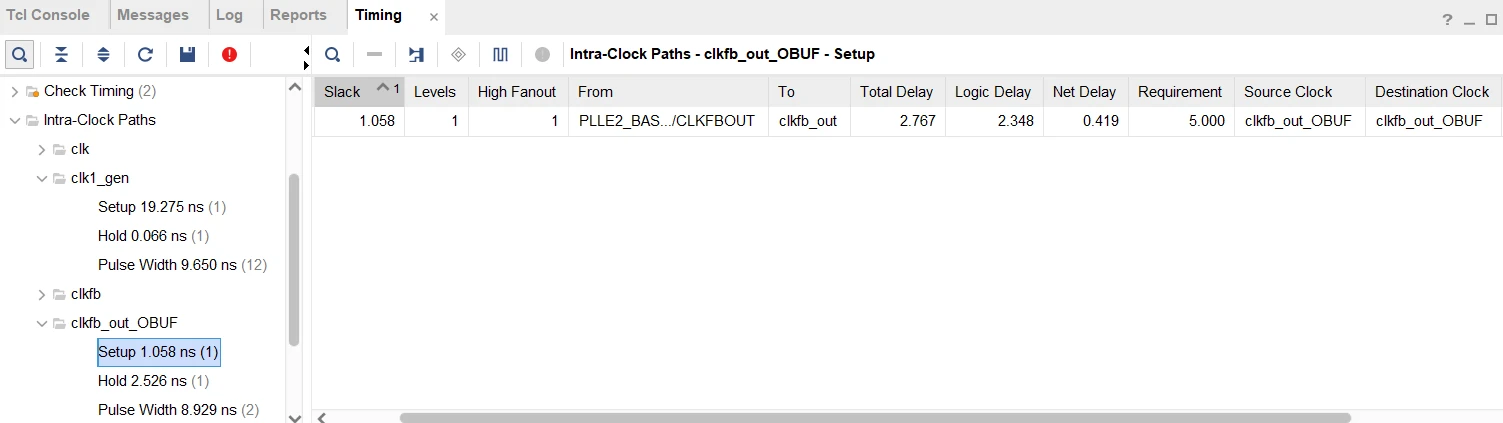

【FPGA】时序概念

目录

一、时钟定义

1.1 Primary Clocks

1.2 Generated Clocks

1.3 Virtual Clock

1.4 Clock groups

二、时钟分类

三、I/O delay约束

四、Timing Exception 一、时钟定义

Primary ClockVirtual ClockGenerated ClockClock groups1.1 Primary Clocks

…

Vivado下组合逻辑模块的仿真

文章目录 与门或门非门异或门同或门比较器半加器全加器乘法器数据选择器3-8 译码器三态门 组合逻辑电路的特点是任意时刻的输出仅仅取决于输入信号,输入信号变化,输出立即变化,其变化不依赖于时钟。 本文中的例子中模块名都是gate,…

Vivado使用入门之三:I/O约束

一、导图概览 二、I/O约束

2.1 I/O约束的内容

I/O约束主要是对port的位置和电气特性进行设置,进入菜单栏Window的IO Ports,可以查看可约束的相关内容。 一些port的常用特性解释如下

Name: port的名称

Direction:port的输入输出类型,有三种…

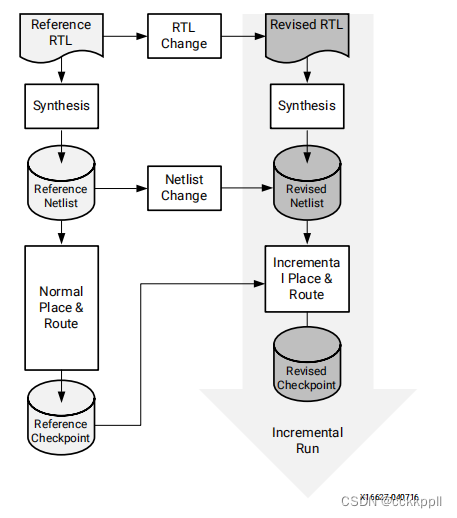

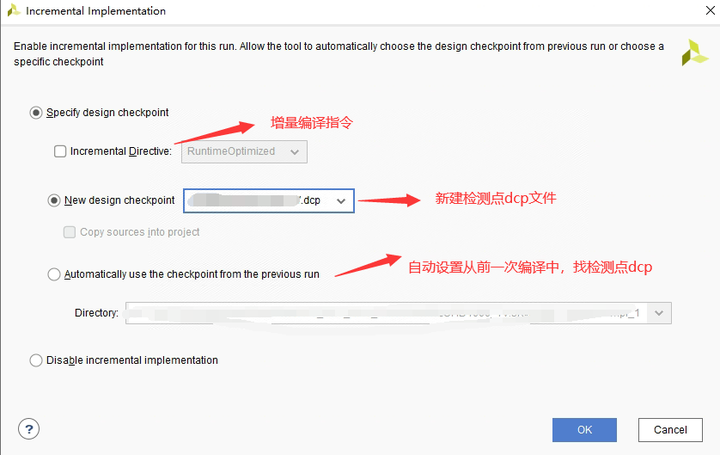

vivado 使用增量实现

使用增量实现

在项目模式和非项目模式中,当使用readcheckpoint-incremental加载参考设计检查点<dcp_file>命令,其中<dcp_file>指定引用的路径和文件名设计检查点。使用-increative选项加载参考设计检查点为后续的放置和布线操作启用增量编译…

vivado 使用远程主机和计算群集

使用远程主机和计算群集 概述 AMD Vivado™集成设计环境(IDE)支持同时并行合成和实现的执行在多个Linux主机上运行。你可以做到这一点通过配置单个主机或指定要在其上启动作业的命令手动执行现有的计算集群。目前,Linux是Vivado唯一支持远程主…

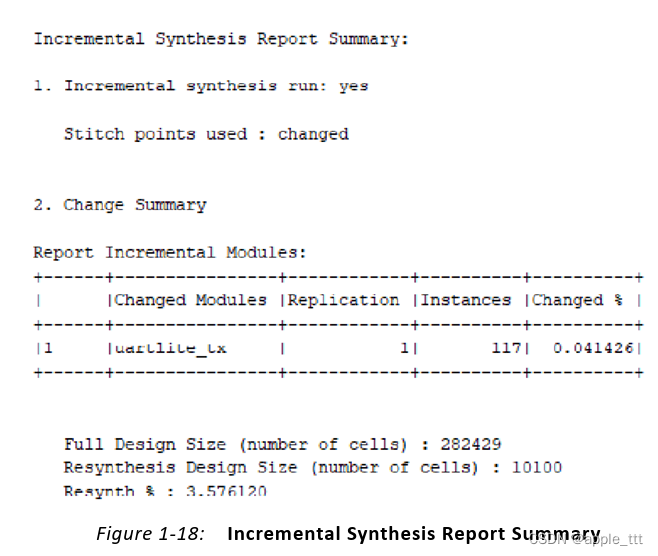

vivado 增量实施

增量实施

增量实现是指增量编译的实现阶段设计流程:

•通过重用参考设计中的先前布局和布线,保持QoR的可预测性。

•加快地点和路线的编制时间或尝试最后一英里的计时关闭。

下图提供了增量实现设计流程图。该图还说明了增量合成流程。有关增量的更多…

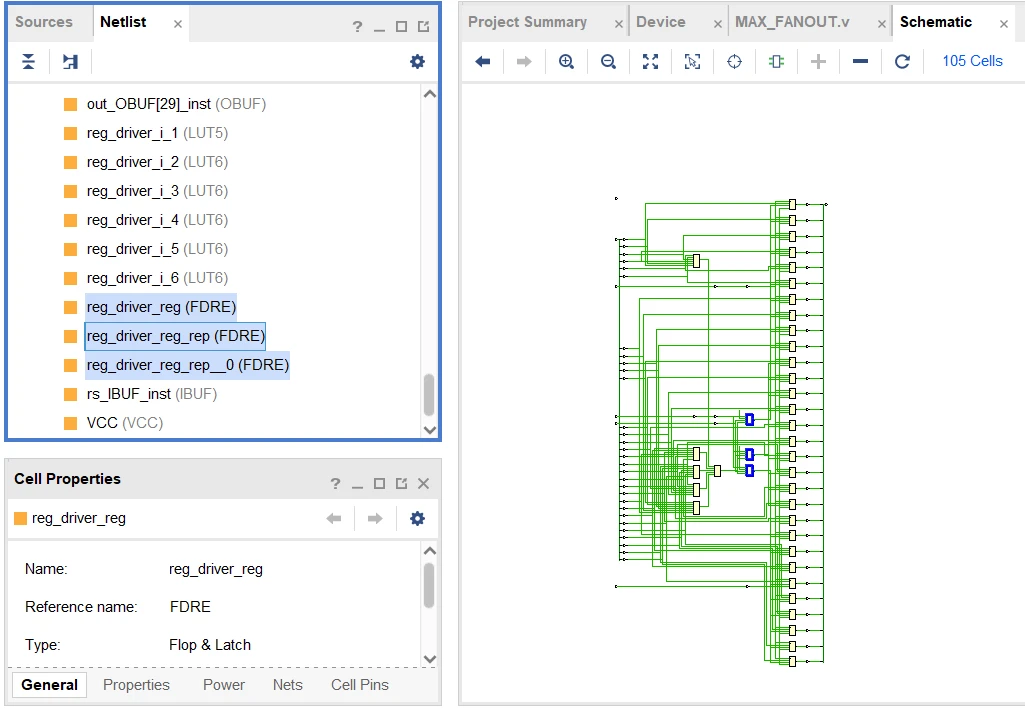

Vivado综合属性系列之六 MAX_FANOUT

目录

一、前言

二、MAX_FANOUT 2.1 工程代码 2.2 工程结果

一、前言 在时序违例的工程中,有一个很常见的原因:高扇出,此时就需要降低信号的扇出,可通过属性MAX_FANOUT来控制信号的扇出值ÿ…

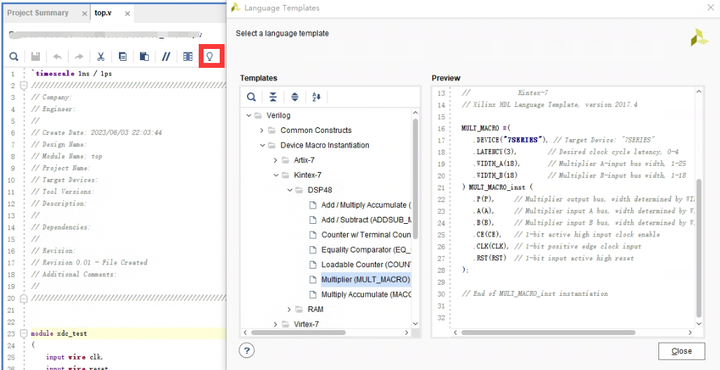

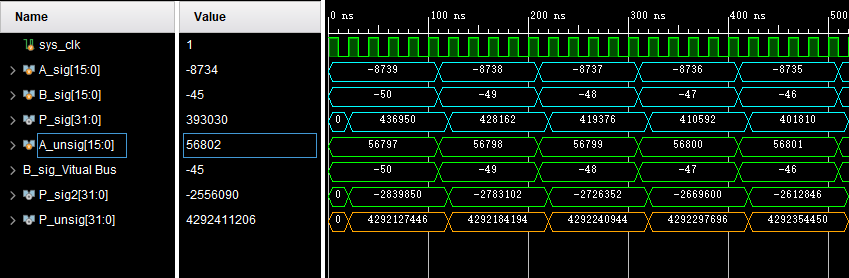

vivado乘法器IP核进行无符号与有符号数相乘问题的验证

本文验证乘法器IP核Multiplier进行无符号(unsigned)与有符号数(signed)相乘的正确性,其中也遇到了一些问题,做此记录。

配套工程:https://download.csdn.net/download/weixin_48412658/88354179 文章目录 问题的讨论验证过程IP核配置例化乘…

Verilog功能模块——同步FIFO

前言 FIFO功能模块分两篇文章,本篇为同步FIFO,另一篇为异步FIFO,传送门:

Verilog功能模块——异步FIFO-CSDN博客

同步FIFO实现起来是异步FIFO的简化版,所以,本博文不再介绍FIFO实现原理,感兴趣…

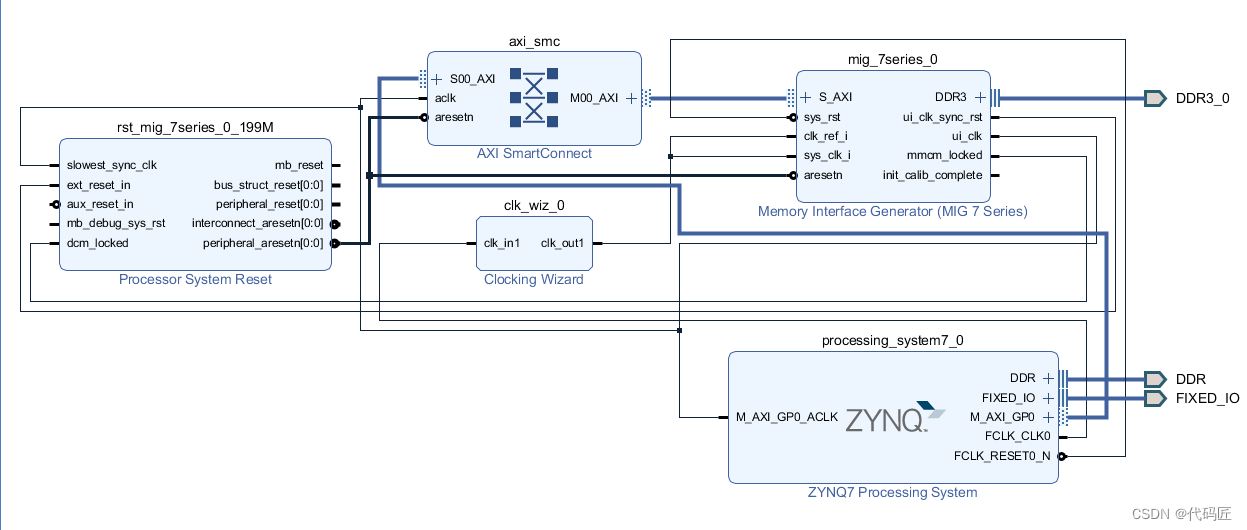

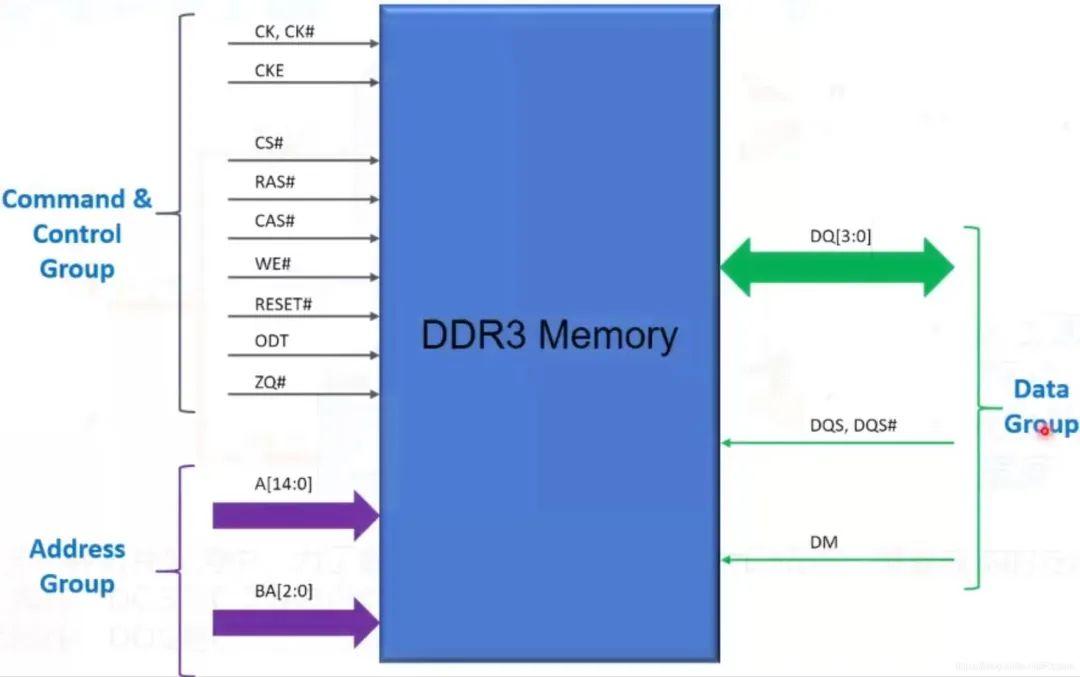

ZYNQ7035 PS读写PL端DDR3

ZYNQ7035 PS读写PL端DDR3

硬件平台

小熊猫嵌入式电子:ZYNQ7035_R5

MIG IP核配置 PL端DDR管脚分配

NET "ddr3_addr[0]" LOC "A8" | IOSTANDARD SSTL15 | VCCAUX_IO NORMAL ;NET "ddr3_addr[…

FPGA设计时序约束十四、Set_External_Delay

一、序言 在时序约束中对clock的约束还存在一种特殊的延时约束set external delay。set external delay如字面含义,设置外部的时延值,但这个外部时延主要是指反馈时延,即信号从FPGA的output端口输出后经过外部电路回到输入端口的时延值。

二…

一个Vivado仿真问题的debug

我最近在看Synopsys的MPHY仿真代码,想以此为参考写个能实现PWM-G1功能的MPHY,并应用于ProFPGA原型验证平台。我从中抽取了一部分代码,用Vivado自带的仿真器进行仿真,然后就遇到了一个莫名其妙的问题,谨以此文作为debug…

vivado $clog2函数

对于.v文件在vivado中是不支持,但是可以修改为.sv或更改文件属性使用sytemverilog来支持。 /*** Math function: $clog2 as specified in Verilog-2005** clog2 0 for value 0* ceil(log2(value)) for value > 1** This implementatio…

Vivado XADC IP核 使用详解

本文介绍Vivado中XADC Wizard V3.3的使用方法。

XADC简介 XADC Wizard Basic

Interface Options: 一共三种,分别是AXI4Lite、DRP、None。勾选后可在界面左侧看到相应通信接口情况。Startup Channel Selection Simultaneous Selection:同时监…

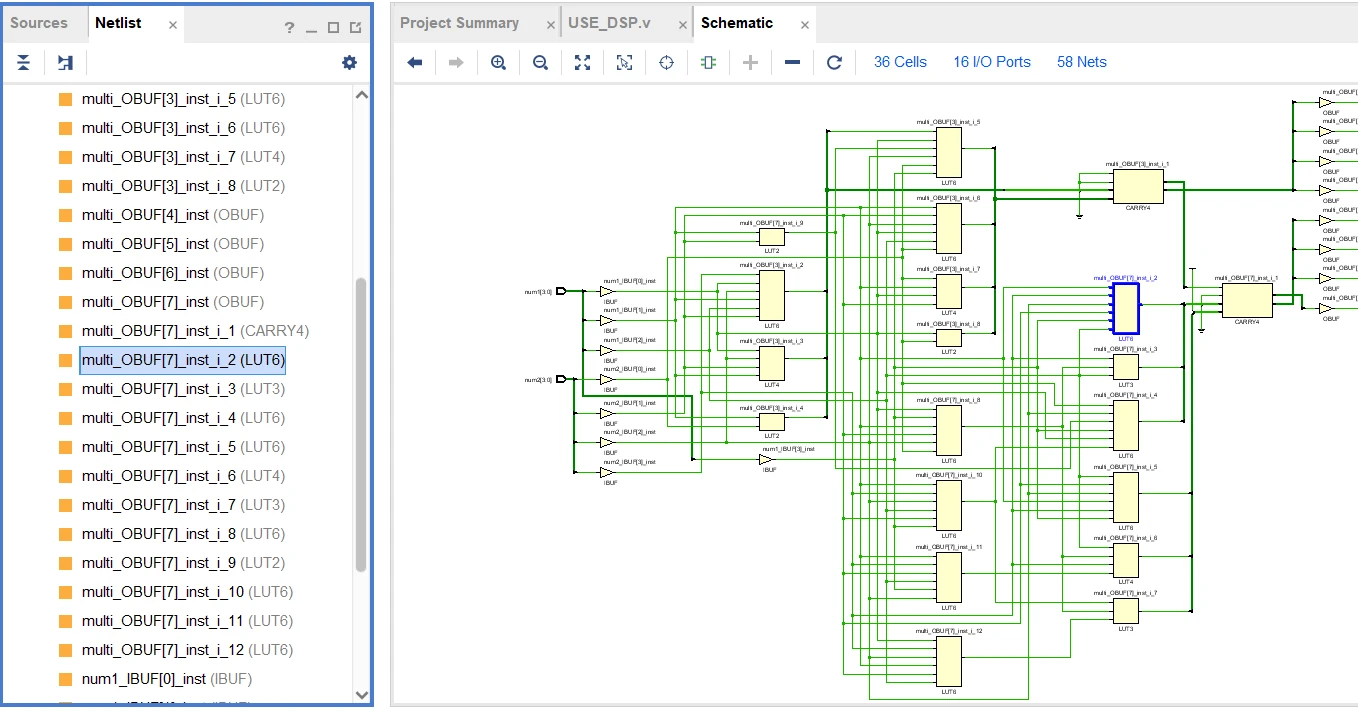

Vivado综合属性系列之五 USE_DSP

目录

一、前言

二、USE_DSP

2.1 工程代码

2.2 结果

2.3 参考资料 一、前言 对于逻辑运算,加、减、乘、除等可以使用逻辑资源LUT实现,也可以使用专用的运算资源DSP来实现。在一些计算量较大时,使用DSP可以节省许多逻辑资源,…

Vivado 使用过程中遇到的问题记录

HLS类IP核综合失败

此IP是HLS类IP核,具体错误如下

Error:[Synth 8-439] module xxx not found

Parameter C_S_AXI_CTRL_ADDR_WIDTH bound to: 32’sb00000000000000000000000000001000 Parameter C_S_AXI_CTRL_DATA_WIDTH bound to: 32’sb000000000000000000000…

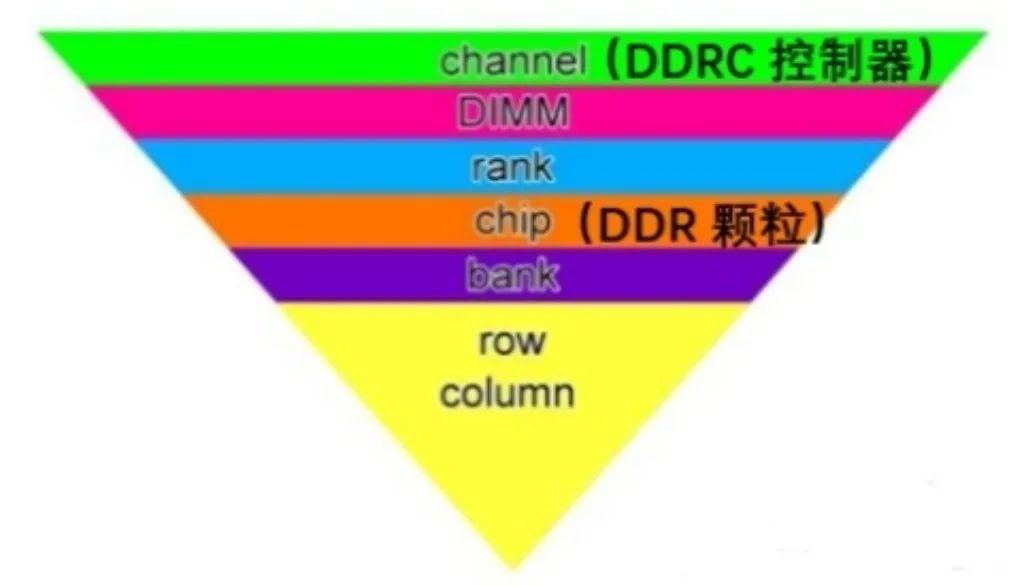

Xilinx FPGA平台DDR3设计详解(三):DDR3 介绍

本文介绍一下常用的存储芯片DDR3,包括DDR3的芯片型号识别、DDR3芯片命名、DDR3的基本结构等知识,为后续掌握FPGA DDR3的读写控制打下坚实基础。

一、DDR3芯片型号

电路板上的镁光DDR3芯片上没有具体的型号名。 如果想知道具体的DDR3芯片型号&#…

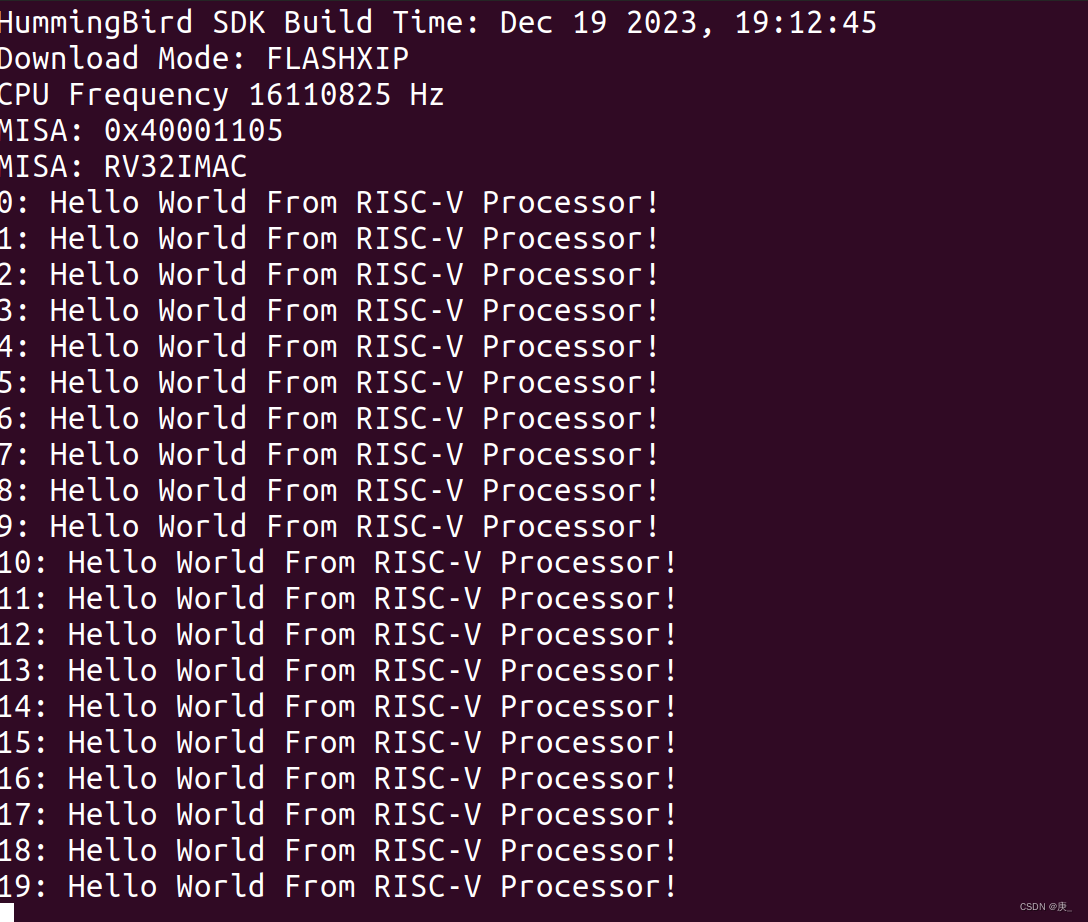

【自用】Ubuntu20.4从Vivado到ddr200t运行HelloWorld

【自用】Ubuntu20.4新系统从输入法到ddr200t运行HelloWorld 一、编辑bashrc二、Vivado2022.2安装三、编译蜂鸟E203自测样例1. 环境准备2. 下载e203_hbirdv2工程文件3. 尝试编译自测案例1. 安装RISC-V GNU工具链2. 编译测试样例 4. 用vivado为FPGA生成mcs文件1.准备RTL2.生成bit…

FPGA设计时序约束八、others类约束之Set_Case_Analysis

目录

一、序言

二、Set Case Analysis

2.1 基本概念

2.2 设置界面

2.3 命令语法

2.4 命令示例

三、工程示例

四、参考资料 一、序言 在Vivado的时序约束窗口中,存在一类特殊的约束,划分在others目录下,可用于设置忽略或修改默认的时序…

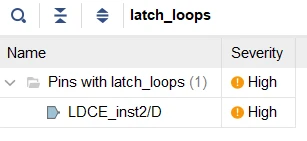

Vivado时序报告之Check_timing详解

目录

一、前言

二、Check_Timing

2.1 含义解释

2.2 工程代码

2.3 时序约束

2.4 Check_timing报告

no clock

pulse_width_clock

unconstrained_internal_endpoints

no_input_delay

no_output_delay

multiple_clock

generated_clocks

loops

partial_input_delay

…

Vivado远程开发探索

平时主要用轻薄本办公,但是有时候又需要用Vivado做一些开发的工作,就感觉生产力不够。如果能在远程的高性能服务器上跑Vivado综合实现就好了。前段时间用ubuntu下安装的Vivado发现有一个Remote Host的设置。所以就准备折腾一下这个。

WSL WSL的安装看官…

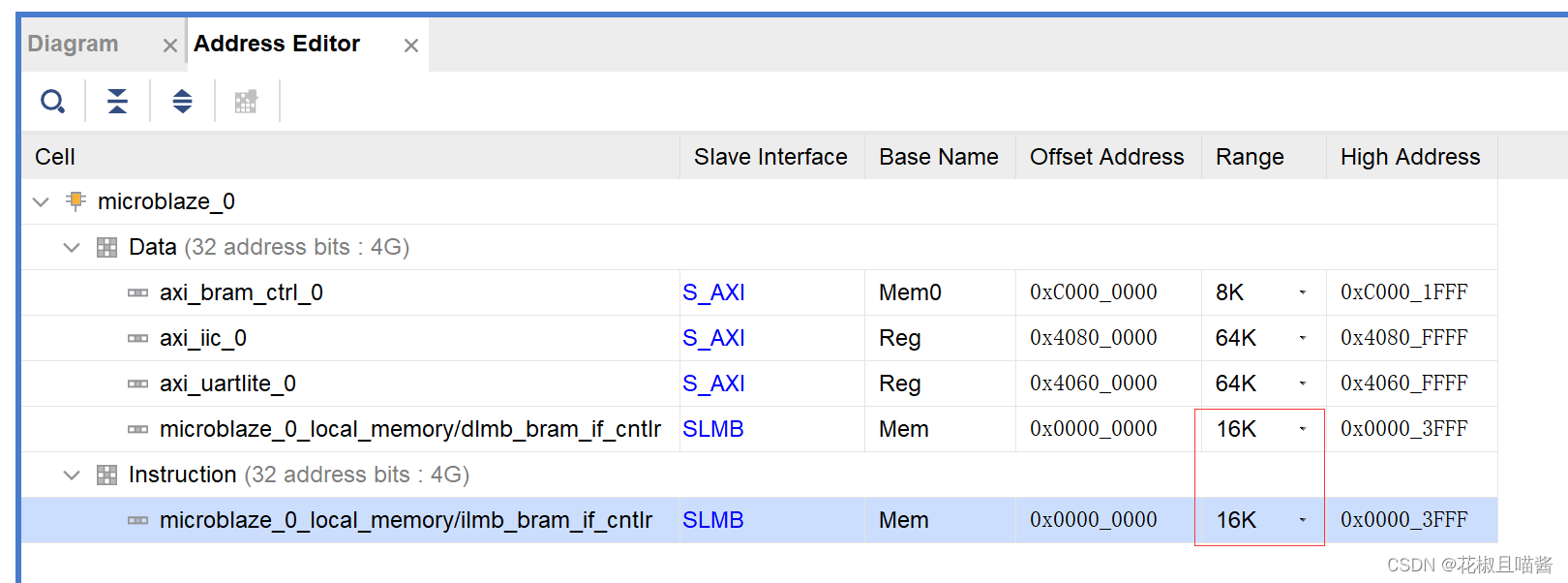

vivado sdk mem超出

Description Resource Path Location Type region microblaze_0_local_memory_ilmb_bram_if_cntlr_Mem_microblaze_0_local_memory_dlmb_bram_if_cntlr_Mem’ overflowed by 4288 bytes uart C/C Problem

问题的产生:fpga使用了microblaze搭建了一个soc系统&#…

【FPGA图像处理实战】- 图像处理前景如何?就业前景如何?

图像处理是FPGA应用的主要领域之一,图像处理数据量特别大且对实时性处理要求高的场景,这恰好能发挥FPGA流水线可实时处理的优势。

那么FPGA图像处理的前景如何?

一、FPGA开发(图像处理)招聘就业情况

看FPGA图像处理前景,最简单的方式--我们去招聘网站上搜一搜,看看招…

【FPGA图像处理实战】- 彩色图像灰度化

今天介绍一下图像处理中的基础算法--彩色图像灰度化。

一、彩色图像处理灰度化

彩色图像灰度化是一种将彩色图像转换为灰度图像的过程。

在RGB模型中,如果R=G=B时,则彩色表示一种灰度颜色,其中R=G=B的值叫灰度值。

因此,灰度图像每个像素只需一个字节存放灰度值(又称强…

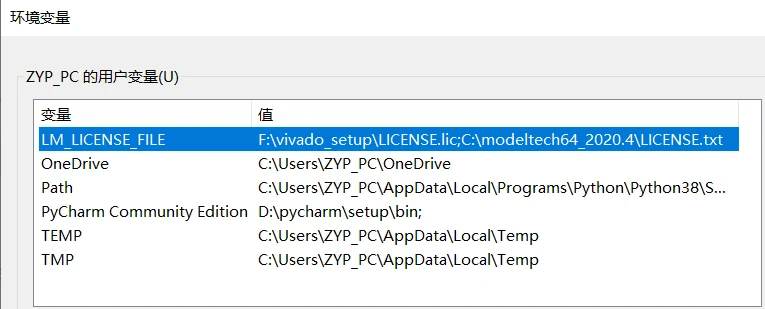

Modelsim仿真问题解疑三:LM_LICENSE_FILE与Vivado命名冲突

现象:

modelsim和Vivado同一时间只能使用一个,另一个会报license相关的错误

原因:

modelsim和Vivado的环境变量名称都为LM_LICENSE_FILE,值配置为其中一个时会导致另一个值被覆盖 解决:

对LM_LICENSE_FILE同时配置modelsim和v…

vivado杂项记录

文章目录 问题的解决Xilinx Vitis 启动时未响应的解决方法Spawn failed:No error错误vivado卡在Initializing Language Server的解决方法vivado中添加文件后出现non-module 其他关于MAX_FANOUT属性vviado 2018.3中IP的core container 问题的解决

Xilinx Vitis 启动…

MicroBlaze系列教程(10):AXI_HWICAP的使用

文章目录 @[toc]1. AXI HWICAP简介2. MicroBlaze硬件配置3. 常用函数4. 使用示例1:读取IDCODE5. 使用示例2:从指定地址重新配置6. 参考资料本文是Xilinx MicroBlaze系列教程的第10篇文章。 1. AXI HWICAP简介

AXI_HWICAP,是把ICAP原语封装成了一个AXI接口的IP核,可以通过M…

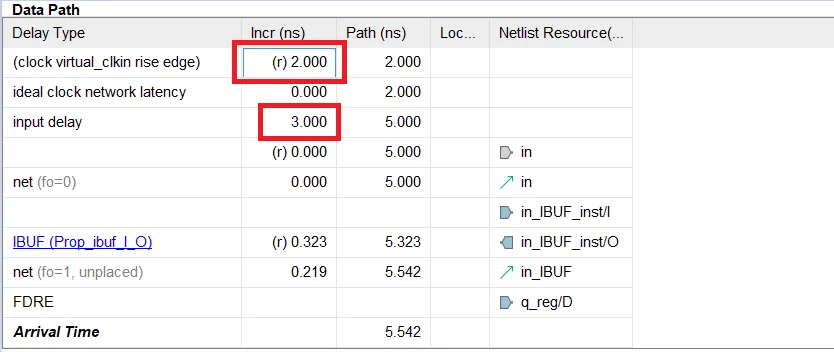

FPGA设计时序约束十六、虚拟时钟Virtual Clock

目录

一、序言

二、Virtual Clock

2.1 设置界面

三、工程示例

3.1 工程设计

3.2 工程代码

3.3 时序报告

3.4 答疑

四、参考资料 一、序言 在时序约束中,存在一个特殊的时序约束,虚拟时钟Virtual Clock约束,根据名称可看出时钟不是实…

vivado报错警告之[Vivado 12-1017] Problems encountered:

文章目录 方法一方法二方法三(作者最终解决) 我们对vivado 的程序进行综合(Run Synthesis)时,可能会出现[Vivado 12-1017] Problems encountered: 1. Failed to delete one or more files in run directory的一个警告信息,导致我们…

Vivado HLS生成IP核报错的解决方案(亲测有效)

ERROR: [IMPL 213-28] Failed to generate IP

使用Vivado HLS过程中点击Export RTL报错 Failed to generate IP,如图所示:

解决方案

下载 Xilinx官网支持社区给出的补丁包 y2k22_patch-1.2.zip,解压到Xilinx安装位置,如图所示…

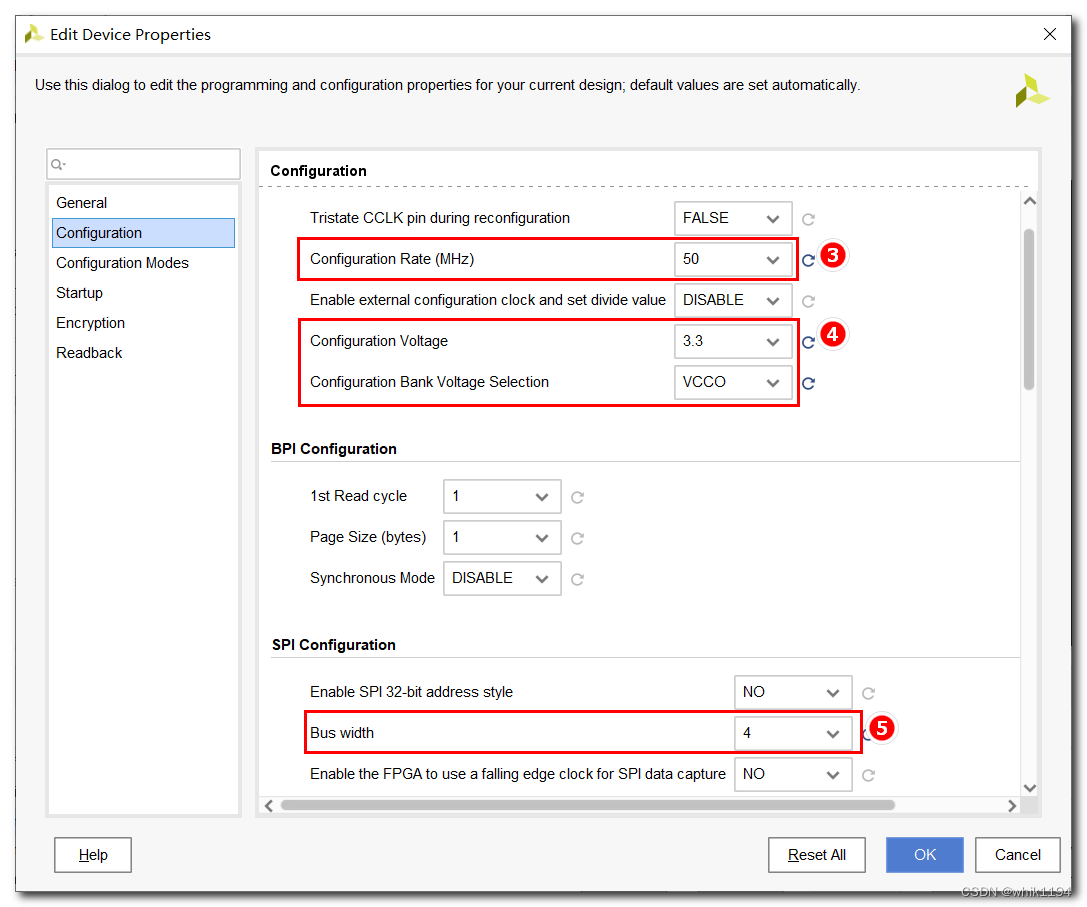

Xilinx FPGA SPIx4 配置速度50M约束语句(Vivado开发环境)

qspi_50m.xdc文件:

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

set_property CONFIG_VOLTAGE 3.3 [curren…

KC705开发板——MGT IBERT测试记录

本文介绍使用KC705开发板进行MGT的IBERT测试。

KC705开发板

KC705开发板的图片如下图所示。FPGA芯片型号为XC7K325T-2FFG900C。

MGT

MGT是 Multi-Gigabit Transceiver的缩写,是Multi-Gigabit Serializer/Deserializer (SERDES)的别称。MGT包含GTP、GTX、GTH、G…

Vivado增量编译:加速FPGA设计实现的利器

随着FPGA设计的复杂度不断提高,设计人员需要选择更为高效的设计流程来保证开发效率和减少开发成本。其中,Vivado增量编译是一种非常重要的设计流程。本文将介绍Vivado增量编译的基本概念、优点、使用方法以及注意事项。

通过阅读本文可以了解࿱…

Vivado如何清理工程,并避免缺失必要的文件?

FPGA开发是一项非常复杂的工作,需要处理大量的代码、约束和仿真文件。在开发过程中,由于文件数量庞大,很容易导致工程变得混乱不堪。Vivado是Xilinx公司推出的一款FPGA开发工具,能够帮助开发人员处理这种复杂性,提高开…

Vivado:ROM和RAM的verilog代码实现

本文主要介绍ROM和RAM实现的verilog代码版本,可以借鉴参考下。

一、ROM设计方法

Read-only memory(ROM)使用ROM_STYLE属性选择使用寄存器或块RAM资源来实现ROM,示例代码如下:

//使用块RAM资源实现ROM

module rams_s…

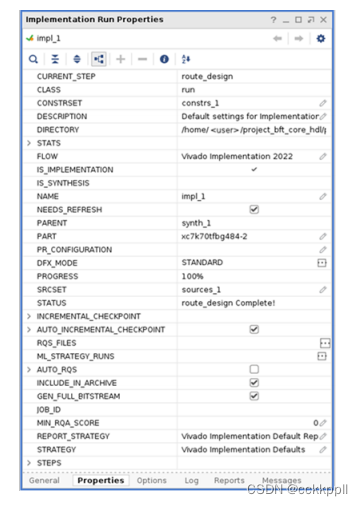

在project模式下自定义Implementation Strategies

Implementation Settings定义了默认选项,当要定义新的implementation runs时会使用这些选项,选项的值可以在Vivado IDE中进行配置。 图1展示了“Settings”对话框中的“implementation runs”对话框。要从Vivado IDE打开此对话框,请从主菜单中…

vivado 高级编程功能1

适用于 7 系列、 UltraScale 和 UltraScale FPGA 和 MPSoC 的回读和验证 为 7 系列器件生成已加密文件和已经过身份验证的文件 注释 : 如需获取其它信息 , 请参阅《使用加密确保 7 系列 FPGA 比特流的安全》 ( XAPP1239 ) 。 要生成加密比特流…

【FIFO】Standard / FWFT FIFO设计实现(二)——异步时钟

标准FIFO 异步FIFO需要使用格雷码同步读写信号,可参考牛客异步FIFO例题,不同于牛客例题之处在于FIFO读空信号置位与FIFO最后一个有效数据输出在同一个周期,与Xilinx FIFO一致。核心代码如下: logic [FIFO_DEPTH_WIDTH : 0] rd_ptr…

vivado 串行矢量格式 (SVF) 文件编程

串行矢量格式 (SVF) 文件编程 注释 : 串行矢量格式 (SVF) 编程在 Versal ™ 器件上不受支持。 对 FPGA 和配置存储器器件进行编程的另一种方法是通过使用串行矢量格式 (SVF) 文件来执行编程。通过 Vivado Design Suite 和 Vivado Lab Edition 生成的 SVF …

vivado ILA 交叉触发

ILA 交叉触发 ILA 交叉触发功能支持在 ILA 核之间以及在 ILA 核与处理器 ( 如 Zynq -7000 SoC ) 之间进行交叉触发。如需在位于不 同时钟域中的 2 个 ILA 核之间执行触发 , 或者要在处理器与 ILA 核之间执行硬件 / 软件交叉触发 &a…

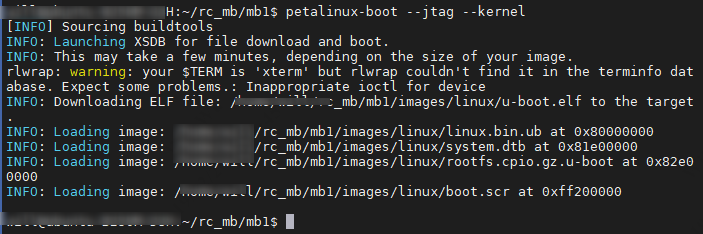

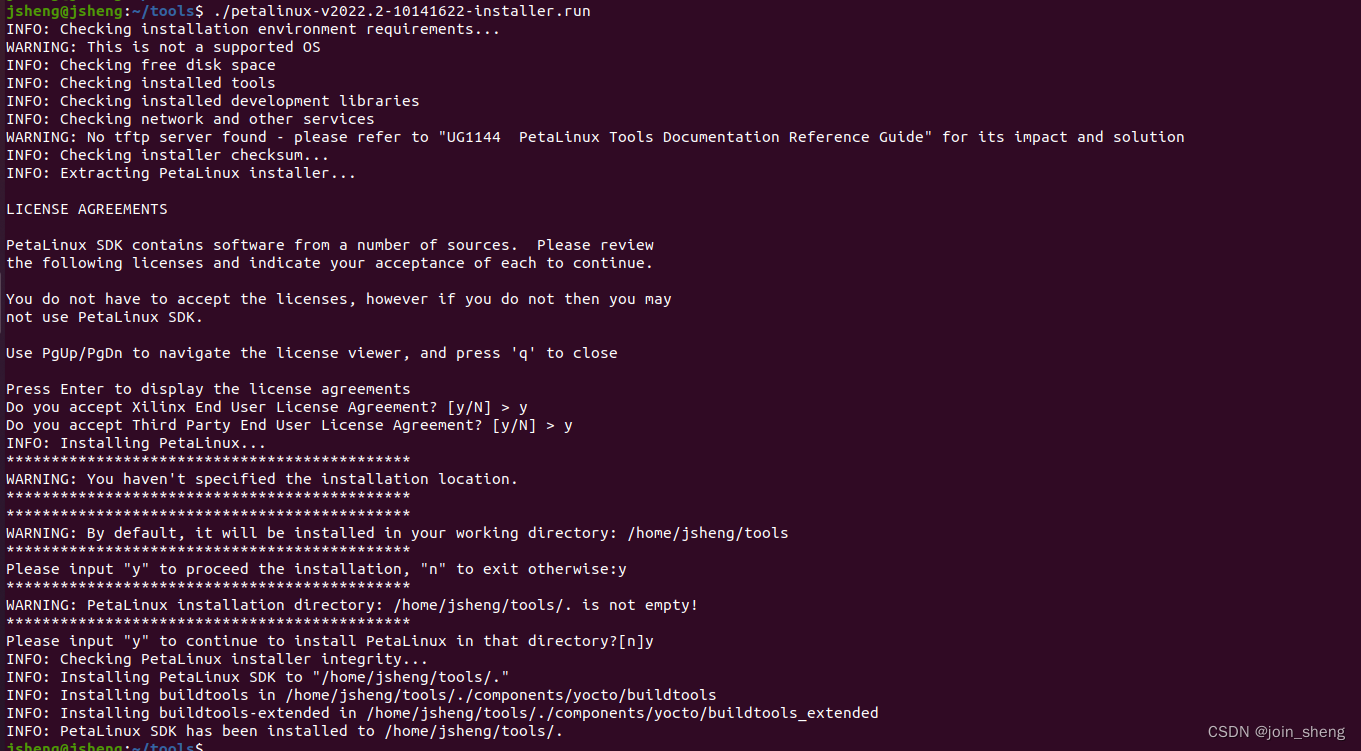

petalinux2022.2在ubantu20.04下的安装

1.Petalinux的下载路径 Downloads 这个是下载petalinux的官网路径。默认是2022.2版本,后期更新的均是以petalinux2022.2版本做的更新。

2.安装流程 在官网下载完成之后,会得到一个名为petalinux-v2022.2-10141622-installer.run的文件,这个文…

Modelsim仿真问题解疑二:ERROR: [USF-ModelSim-70]

现象:在Vivado中已配置modelsim为仿真工具后,运行仿真,报错USF-ModelSim-70和ERROR: [Vivado 12-4473]

详细报错内容如下

ERROR: [USF-ModelSim-70] compile step failed with error(s) while executing C:/Users/ZYP_PC/Desktop/verilog_t…

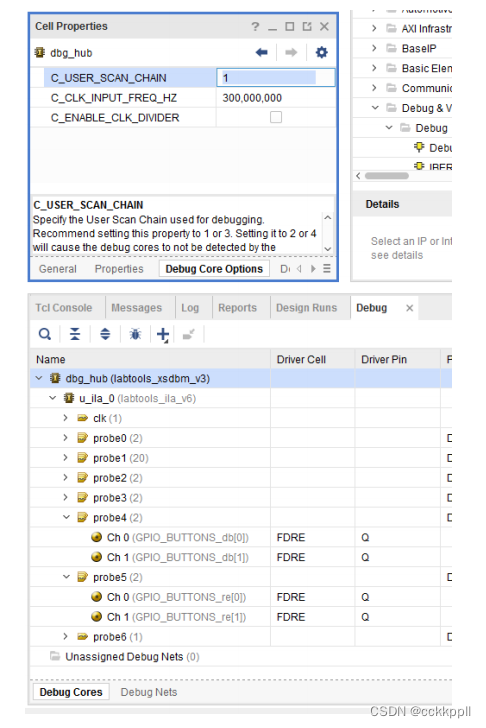

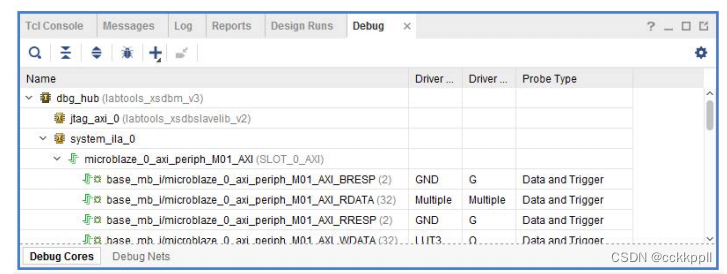

vivado IP integrator 中的调试流程

IP integrator 中的调试流程 Vivado IP integrator 中的 System ILA IP 允许您对 FPGA 或 ACAP 上的实现后设计执行系统内调试。如需监控 IP integrator 块设计中的接口和信号 , 请使用此功能。此功能支持您在 Vivado 硬件管理器中对 AXI 读写、数据和地址…

使用Vivado Design Suite进行物理优化(二)

物理优化是对设计的negative-slack路径进行时序驱动的优化。而phys_opt_design 命令是用于对设计进行物理优化。这个命令可以在布局后的后置模式(post-place mode)中运行,也就是在放置所有组件之后;还可以在完全布线后的后置模式&…

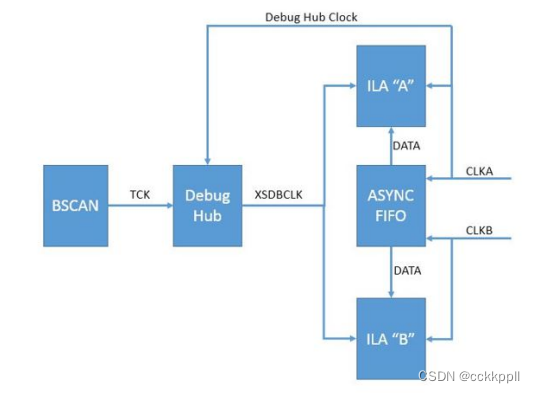

vivado 调试核时钟设置指南

调试核时钟设置指南 注释 : 以下章节适用于 7 系列、 UltraScale 和 UltraScale 器件。 Versal 调试核使用基于 AXI 的连接 , 且不受本章中的 时钟设置指南的约束。 Vivado 硬件管理器使用 JTAG 接口来与 Vivado Debug Hub 核进行通信 &#…

使用Vivado Design Suite进行功率优化

功率优化是一个可选步骤,它通过使用时钟门控来优化动态功率。它既可以在Project模式下使用,也可以在Non-Project模式下使用,并且可以在逻辑优化之后或布局之后运行,以减少设计中的功率需求。功率优化包括Xilinx的智能时钟门控解决…

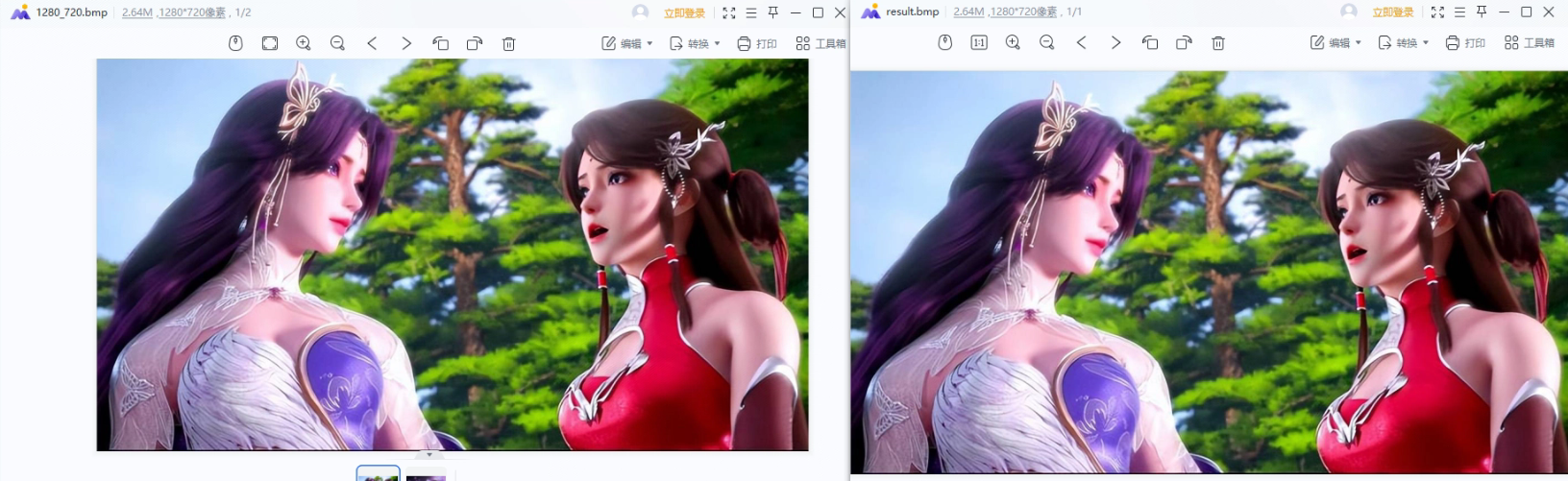

【FPGA图像处理实战】- FPGA图像处理仿真测试工程(读写BMP图片)

FPGA开发过程中“行为功能仿真”是非常必要的一个过程,如果仿真都没通过,则上板测试必定失败。

FPGA图像处理需要读写大量的图像数据,单看这些图像数据实际是没有规则的,如果直接上板测试,调试起来非常困难࿰…

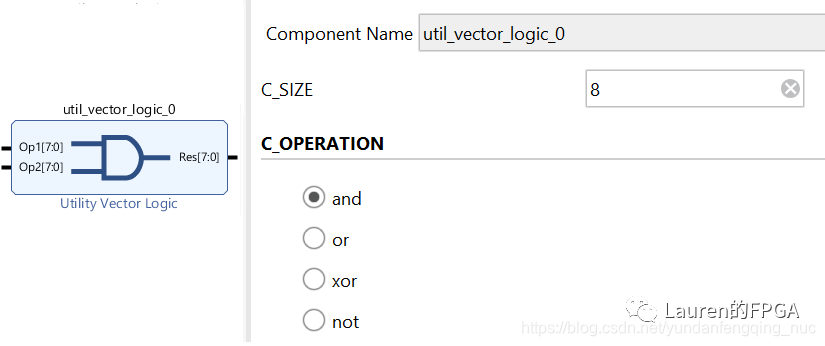

vivado常见IP介绍

转自:微信公众号:Lauren的FPGA 目前,越来越多的工程师会用到Vivado IP Integrator(IPI)。它的强大之处在于通过实例化和互连IP构建复杂的设计。现在的IPI中,不仅可以添加Vivado IP,还可以添加用…

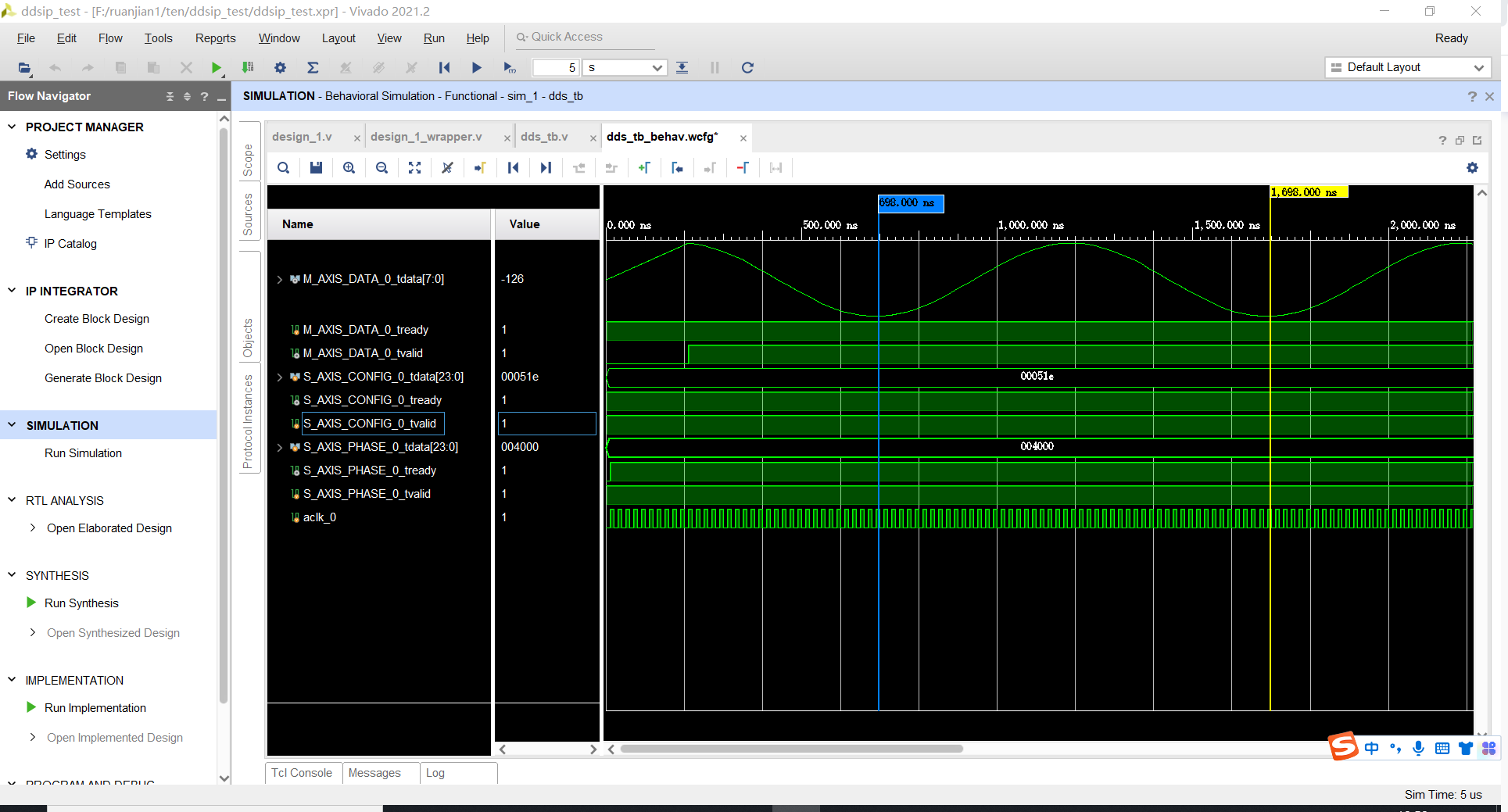

基于vivado DDS ip核的DDS信号发生器(可调频调相)

基于Vivado DDS ip核的DDS信号发生器: 在Vivado软件中调出DDS ip核进行设置,很多参数可以参考xilinx官方手册,比较重要的是System Clock系统时钟和Phase Widh相位宽度的设置,这是最终得到波形的频率和相位所需要的基础参数&#x…

vivado综合出现[Synth 8-91] ambiguous clock in event control

vivado综合出现[Synth 8-91] ambiguous clock in event control查阅相关资料,目前有两种情况:1.always敏感变量没有得到使用 常见有rst信号代码修改如下即可:2.always块中语法问题敏感变量都有使用,为何还会出现该问题,…

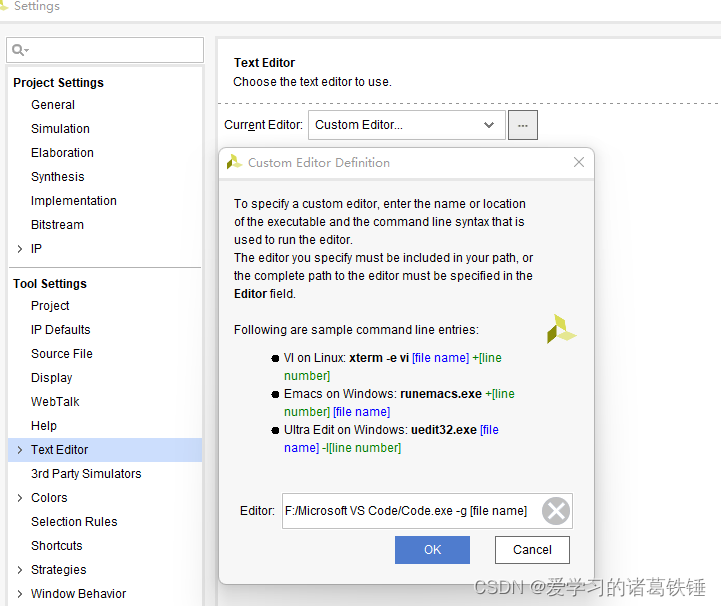

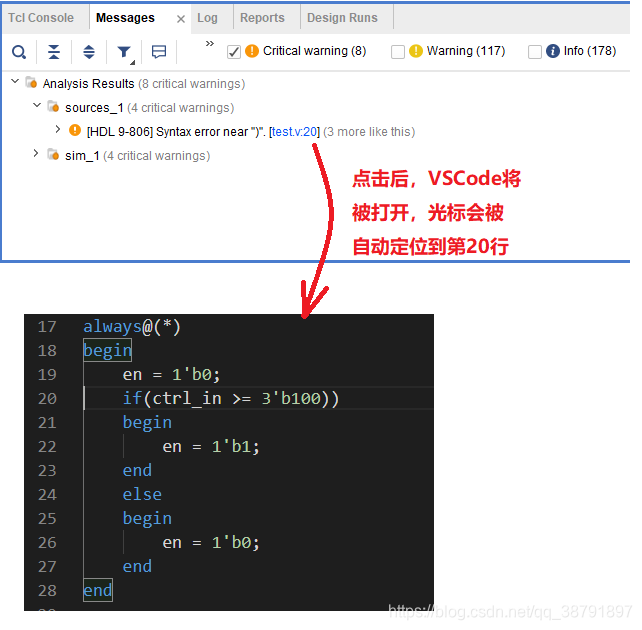

教程:在Vivado中指定VSCode作为文本编辑器

教程:在Vivado中指定VSCode作为文本编辑器 更新历史 20190325: 首次发布 20201027: 对本文第三步中需要填写的内容做了修改,使得VSCode能够实现光标的自动定位。该修改的做法是“HK Journalist”在评论中指出的。在此表示感谢。针…

Vivado使用(6)——增量综合( Incremental Synthesis)

目录

一、概述

1.1 增量综合的工作原理

1.2 增量综合的优点

1.3 注意事项

二、设置增量综合

2.1 Write Incremental Synthesis 复选框

2.2 Incremental Synthesis 选择框

2.2.1 自动使用上一次运行的检查点(Automatically use the checkpoint from the…

vivado 配置存储器器件编程2

为双 QSPI (x8) 器件创建配置存储器文件 您可使用 write_cfgmem Tcl 命令来为双 QSPI (x8) 器件生成 .mcs 镜像。此命令会将配置数据自动拆分为 2 个独立 的 .mcs 文件。 注释 : 为 SPIx8 生成 .mcs 时指定的大小即为这 2 个四通道闪存器件的总大小。…

超详细-Vivado配置Sublime+Sublime实现VHDL语法实时检查

目录

一、前言

二、准备工作

三、Vivado配置Sublime

3.1 Vivado配置Sublime

3.2 环境变量添加

3.3 环境变量验证

3.4 Vivado设置

3.5 配置验证

3.6 解决Vivado配置失败问题

四、Sublime配置

4.1 Sublime安装Package Control

4.2 Sublime安装VHDL插件

4.3 语法检查…

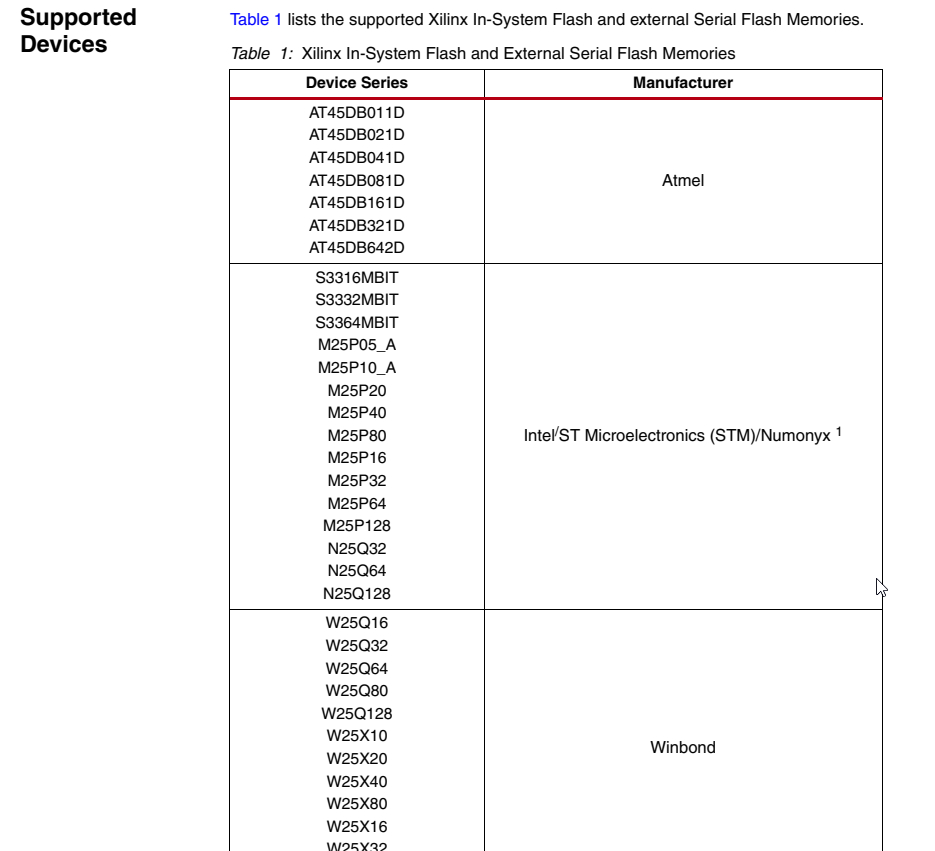

MicroBlaze系列教程(9):xilisf串行Flash驱动库的使用

文章目录 1. xilisf库简介2. xilisf库函数3. xilisf配置4. xilisf应用示例工程下载本文是Xilinx MicroBlaze系列教程的第9篇文章。 1. xilisf库简介

xilisf库(Xilinx In-system and Serial Flash Library) 是Xilinx 提供的一款串行Flash驱动库,支持常用的 Atmel 、Intel、S…

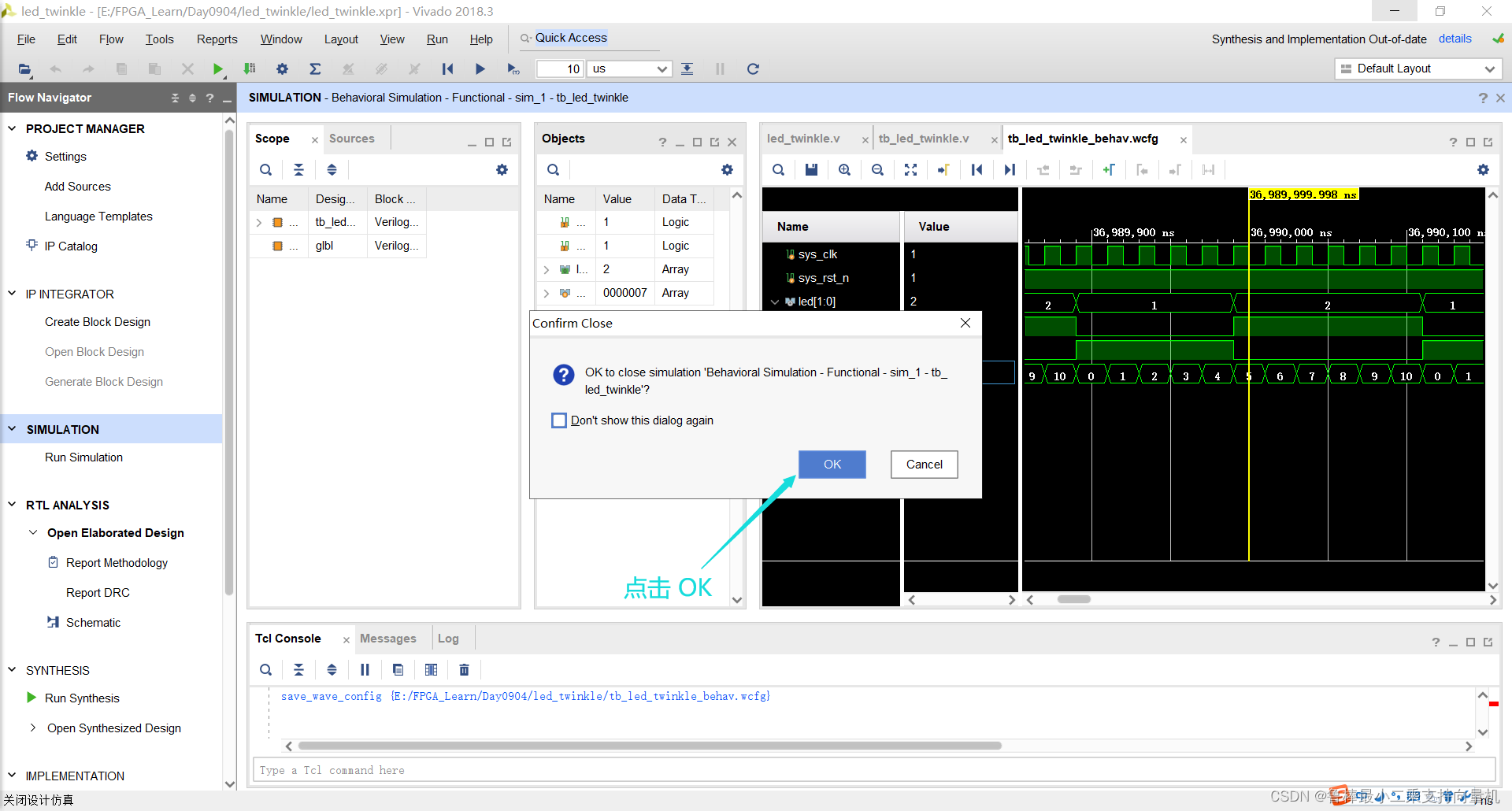

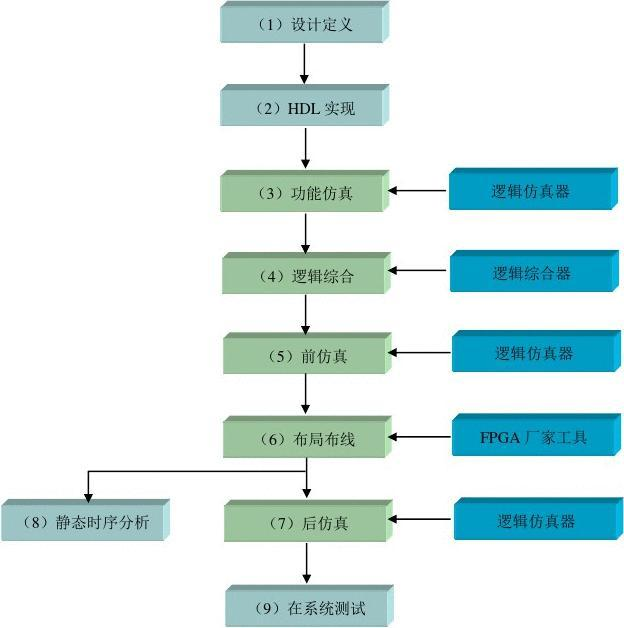

ZYNQ之FPGA学习----Vivado功能仿真

1 Vivado功能仿真

阅读本文需先学习: FPGA学习----Vivado软件使用

典型的FPGA设计流程,如图所示: 图片来自《领航者ZYNQ之FPGA开发指南》

Vivado 设计套件内部集成了仿真器 Vivado Simulator,能够在设计流程的不同阶段运行设计的功能仿真和…

[FPGA IP系列] FPGA常用存储资源大全(RAM、ROM、CAM、SRAM、DRAM、FLASH)

本文主要介绍FPGA中常用的RAM、ROM、CAM、SRAM、DRAM、FLASH等资源。

一、RAM

RAM(Random Access Memory)是FPGA中最基本和常用的内部存储块,根据不同架构可以实现不同容量,最大可达几十Mb。

FPGA中的RAM主要包括: 分布式RAM:存在于逻辑块…

vivado使用其他route_design选项、

使用其他route_design选项

以下是有关route_design选项和选项值(如适用)的更多详细信息。

•-nets:这将操作限制为仅指定的网络列表。该选项需要一个参数即网络对象的Tcl列表。请注意,参数必须是一个net对象,值由get…

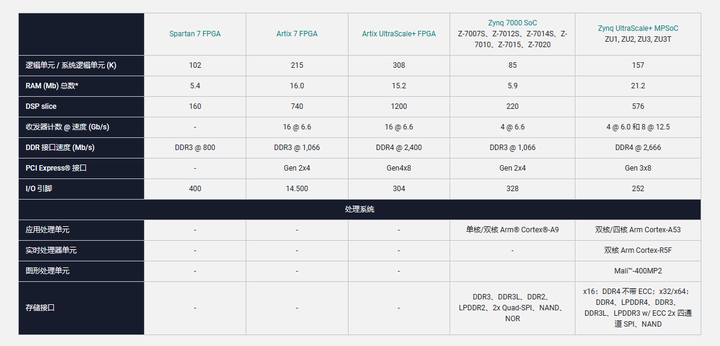

如何选对适合你的FPGA?快速掌握选型技巧!

FPGA厂家和芯片型号众多,在开发过程中,特别是新产品新项目时,都会面临FPGA选型的问题。

如何选择出适合的FPGA型号非常关键,需要评估需求、功能、成本、存储器、高速收发器等各种因素,选出性能与成本平衡的FPGA芯片。…

Vivado下时序逻辑模块的仿真

文章目录 D触发器两级D触发器带异步复位的D触发器带异步复位和同步置数的D触发器移位寄存器单口RAM伪双口RAM真双口RAM单口ROM 组合逻辑电路在逻辑功能上特点是任意时刻的输出仅仅取决于当前时刻的输入,与电路原来的状态无关。 时序逻辑在逻辑功能上的特点是任意时刻…

FPGA使用MIG调用SODIMM内存条接口教程,提供vivado工程源码和技术支持

目录 1、前言免责声明 2、SODIMM内存条简介3、设计思路框架视频输入视频缓存MIG配置调用SODIMM内存条VGA时序视频输出 4、vivado工程详解5、上板调试验证6、福利:工程代码的获取 1、前言

FPGA应用中,数据缓存是一大重点,不管是图像处理还是A…

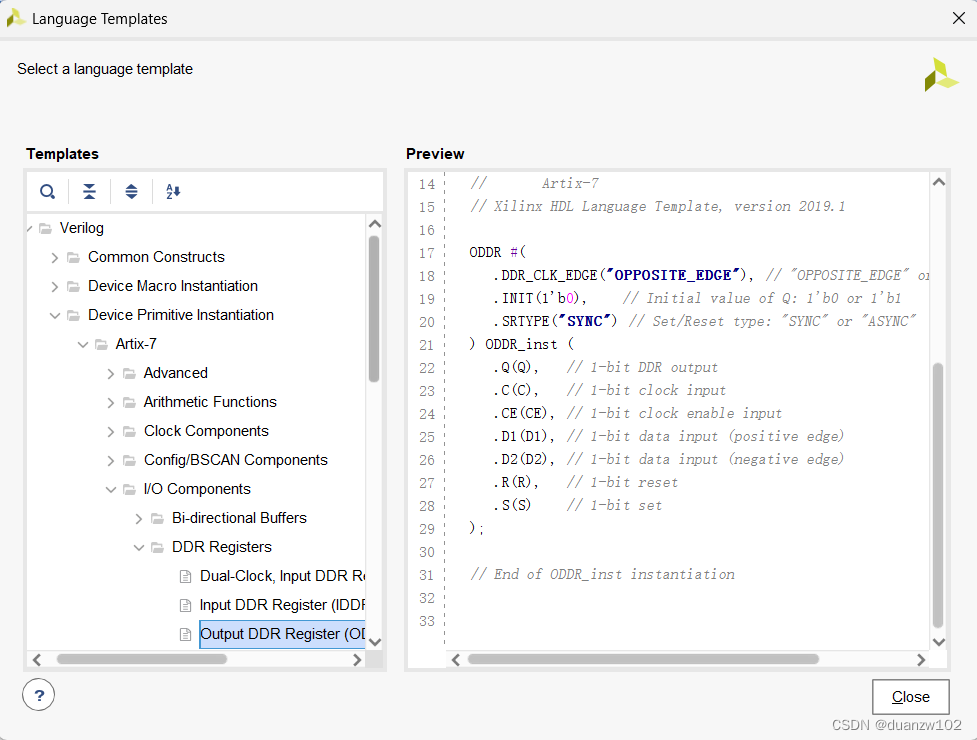

Vivado原语模板

1.原语的概念 原语是一种元件! FPGA原语是芯片制造商已经定义好的基本电路元件,是一系列组成逻辑电路的基本单元,FPGA开发者编写逻辑代码时可以调用原语进行底层构建。 原语可分为预定义原语和用户自定义原语。预定义原语为如and/or等门级原语…

vivado 启动实施运行

启动实施运行

您可以启动活动的实现运行,也可以选择同时启动多个运行。

启动单个实施运行

执行以下任意操作以在“设计运行”窗口中启动活动的实现运行。启动单个实现运行将为实现启动一个单独的过程。

提示:在“设计运行”窗口中选择一个运行&#…

FPGA开发基本流程详解

FPGA是一种可编程逻辑器件,与传统的硬连线电路不同,它具有高度的可编程性和灵活性。FPGA的设计方法包括硬件设计和软件设计两部分,硬件设计包括FPGA芯片电路、存储器、输入输出接口电路等等,软件设计则是HDL程序开发,以…

【XILINX】记录ISE/Vivado使用过程中遇到的一些warning及解决方案

前言 XILINX/AMD是大家常用的FPGA,但是在使用其开发工具ISE/Vivado时免不了会遇到很多warning,(大家是不是发现程序越大warning越多?),并且还有很多warning根据消除不了,看着特心烦? 我这里汇总一些我遇到的…

Vivado Vitis 2023.2 环境配置 Git TCL工程管理 MicroBlaze和HLS点灯测试

文章目录 本篇概要Vivado Vitis 环境搭建Vivado 免费标准版 vs 企业版Vivado Windows 安装Vivado 安装更新 Vivado 工程操作GUI 创建工程打开已有工程从已有工程创建, 重命名工程GUI导出TCL, TCL复原工程TCL命令 Vivado 版本控制BlinkTcl脚本新建导出重建工程纯Verilog BlinkTc…

一起学习用Verilog在FPGA上实现CNN----(二)卷积层设计

1 打开Vivado工程

Vivado工程文件如图: 打开Vivado软件,打开工程,如图: 自动升级到当前版本,如图: 暂时选择现有开发板的型号,如图: 出现一条警告性信息,暂时先不管&…

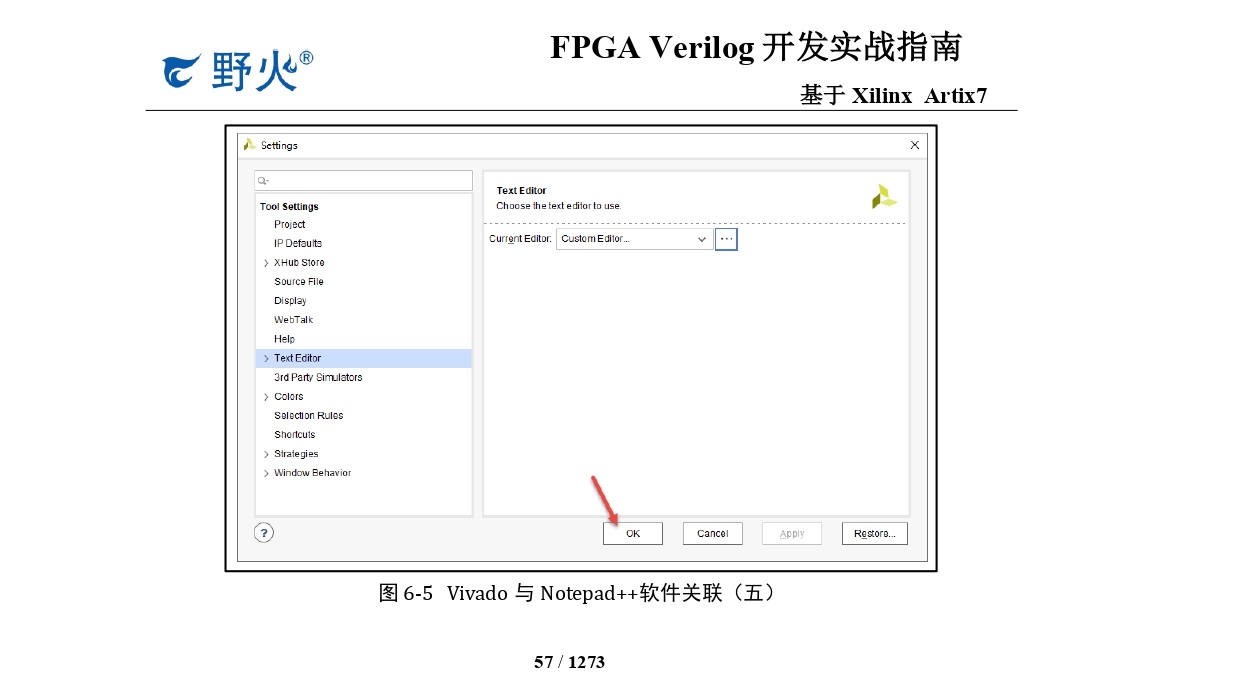

Vivado与Notepad++关联步骤

填写内容

先看"关联步骤"再看此处:

在“editor”栏中填写 Notepad的路径,并加上[file name] -n[line number], 这里我的 Notepad 的路径为 C:/Program Files (x86)/Notepad/notepad.exe ; 故这里我就填上以下内容即可…

ZYNQ——脉宽调制之呼吸灯实现

文章目录 原理简介实验代码软件仿真板上验证 原理简介

呼吸灯的实现过程就是把不同占空比的脉冲输出后加在LED上,LED灯就会显示不同的亮度,通过不断地调节方波的占空比,LED灯的亮度也会跟着变化,看起来就像是“呼吸”一样。 要得…

Xilinx FPGA管脚约束语法规则(UCF和XDC文件)

文章目录 1. ISE环境(UCF文件)2. Vivado环境(XDC文件) 本文介绍ISE和Vivado管脚约束的语句使用,仅仅是管脚和电平状态指定,不包括时钟约束等其他语法。

ISE使用UCF文件格式,Vivado使用XDC文件&…

Xilinx FPGA 超温关机保护

在UG480文档,有关于FPGA芯片热管理的介绍。 首先需要理解XADC中的 Over Temperature(OT)和User Temperature的关系。片上温度测量用于关键温度警告,也支持自动关机,以防止设备被永久损坏。片上温度测量在预配置和自动关…

Vivado下阻塞赋值和非阻塞赋值的对比

Verilog 基础知识 中已经介绍过了阻塞赋值和非阻塞赋值的区别,下面通过一个在Vivado中的简单例子来直观的反映两者的不同。 首先给出设计源代码如下。

module block(a,b,c,clk,x);input x;input clk;output reg a,b,c;always(posedge clk)

begina x; //阻塞赋值…

Vivado中VIO IP核的使用

Vivado中VIO IP核的使用一、写在前面二、VIO IP核配置三、VIO联调四、写在后面一、写在前面 Vivado中的VIO(Virtual Input/Output) IP核是一种用于调试和测试FPGA设计的IP核。它允许设计者通过使用JTAG接口读取和写入FPGA内部的寄存器,从而检…

FPGA设计时序约束十三、Set_Data_Check

目录

一、序言

二、Set Data Check

2.1 基本概念

2.2 设置界面

2.3 命令语法

三、工程示例

3.1 工程代码

3.2 约束设置

3.3 时序报告

四、参考资料 一、序言 通常进行时序分析时,会考虑触发器上时钟信号与数据信号到达的先后关系,从而进行setu…

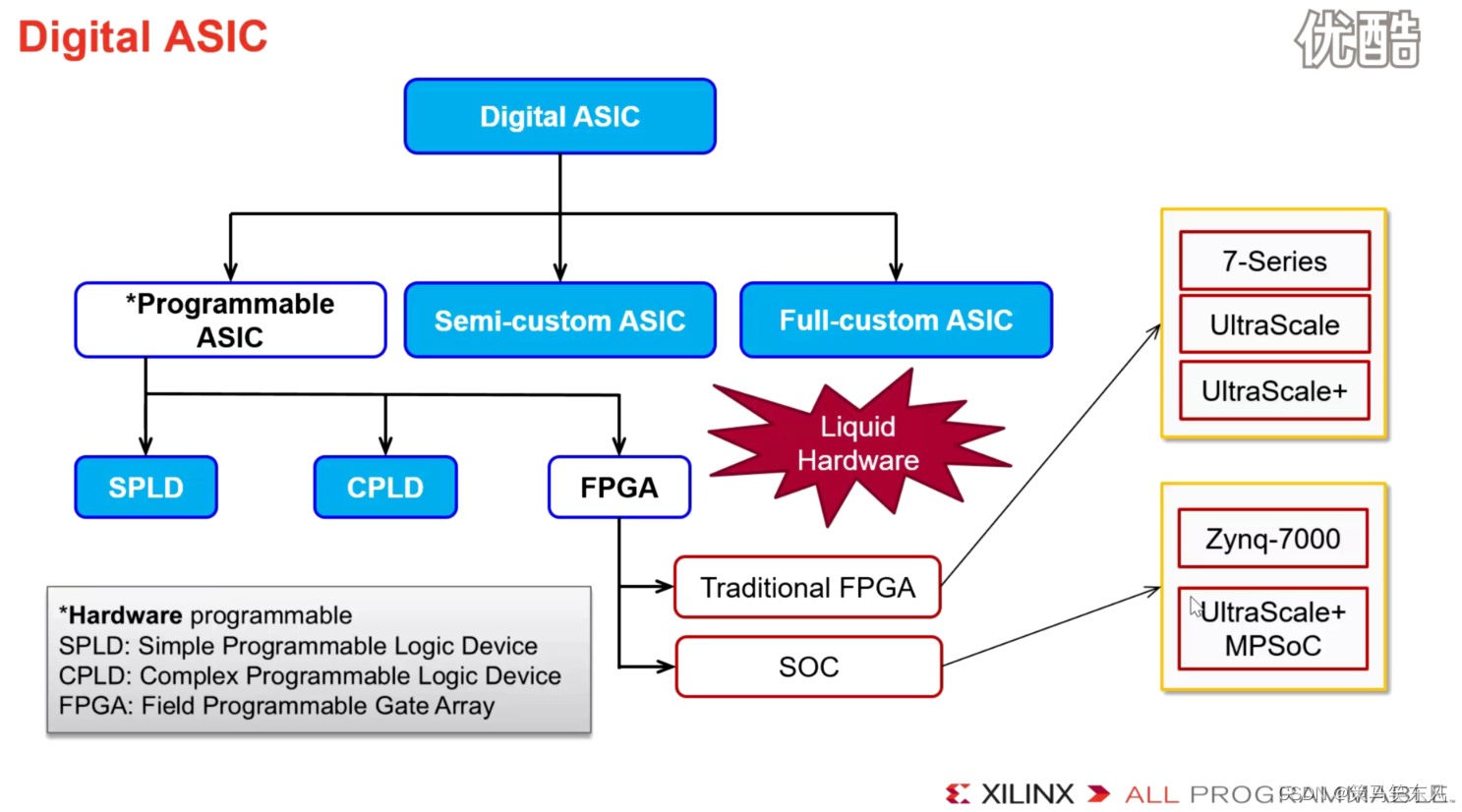

Vivado HLS 第1讲 软件工程师该怎么了解FPGA架构

Vivado HLS是将基于C/C++描述的算法转化成相应的RTL代码,最终在FPGA上实现。这就要求软件工程师对FPGA的内部架构有一些基本的认识,目的在于保证生成的RTL代码在性能和资源上能够达到很好的平衡。实际上,C语言与FPGA是有一些对应关系的。比如:

C语言中的数组可对应于FPGA中…

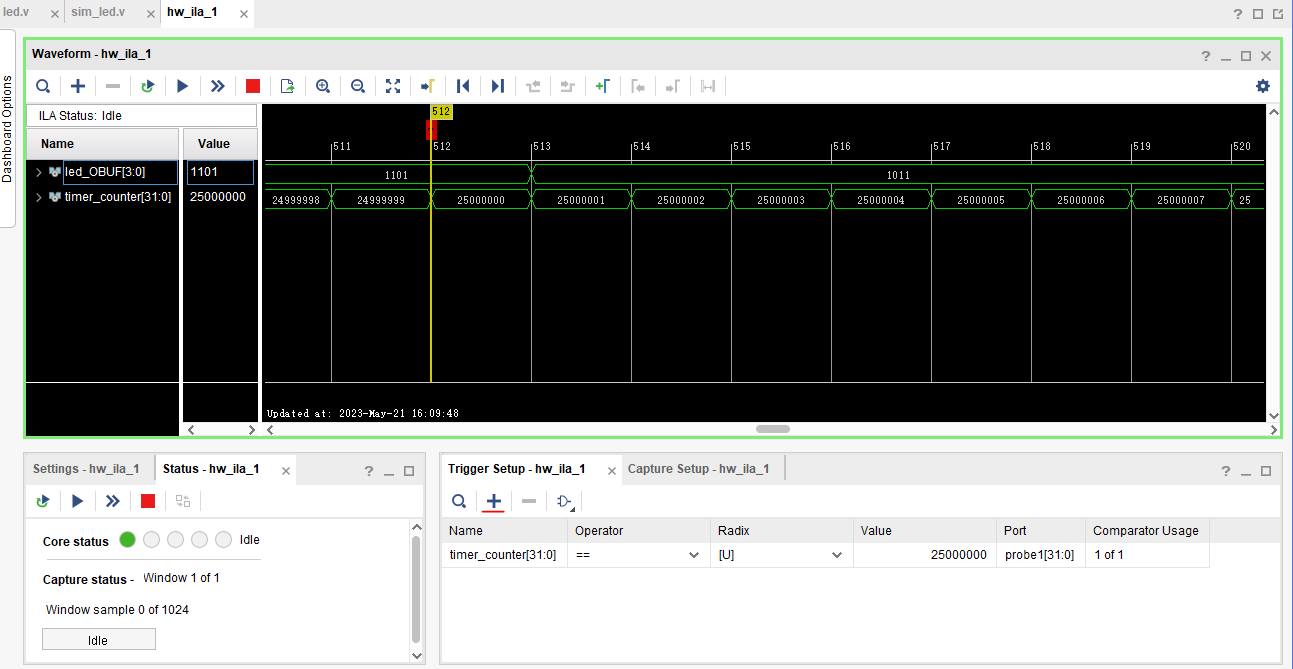

ZYNQ——PL端流水灯的实现

文章目录 一、介绍二、代码编写三、引脚分配四、仿真分析五、添加 ILA IP六、板上验证 一、介绍

本文介绍的是在ZYNQ 7020黑金开发板上实现PL端流水灯的例子,开发板上PL端的LED灯总共有4个,在原理图中找到 PL LED 如下图所示,通过看图可知&a…

[FPGA IP系列] BRAM IP参数配置与使用示例

FPGA开发中使用频率非常高的两个IP就是FIFO和BRAM,上一篇文章中已经详细介绍了Vivado FIFO IP,今天我们来聊一聊BRAM IP。

本文将详细介绍Vivado中BRAM IP的配置方式和使用技巧。

一、BRAM IP核的配置

1、打开BRAM IP核

在Vivado的IP Catalog中找到B…

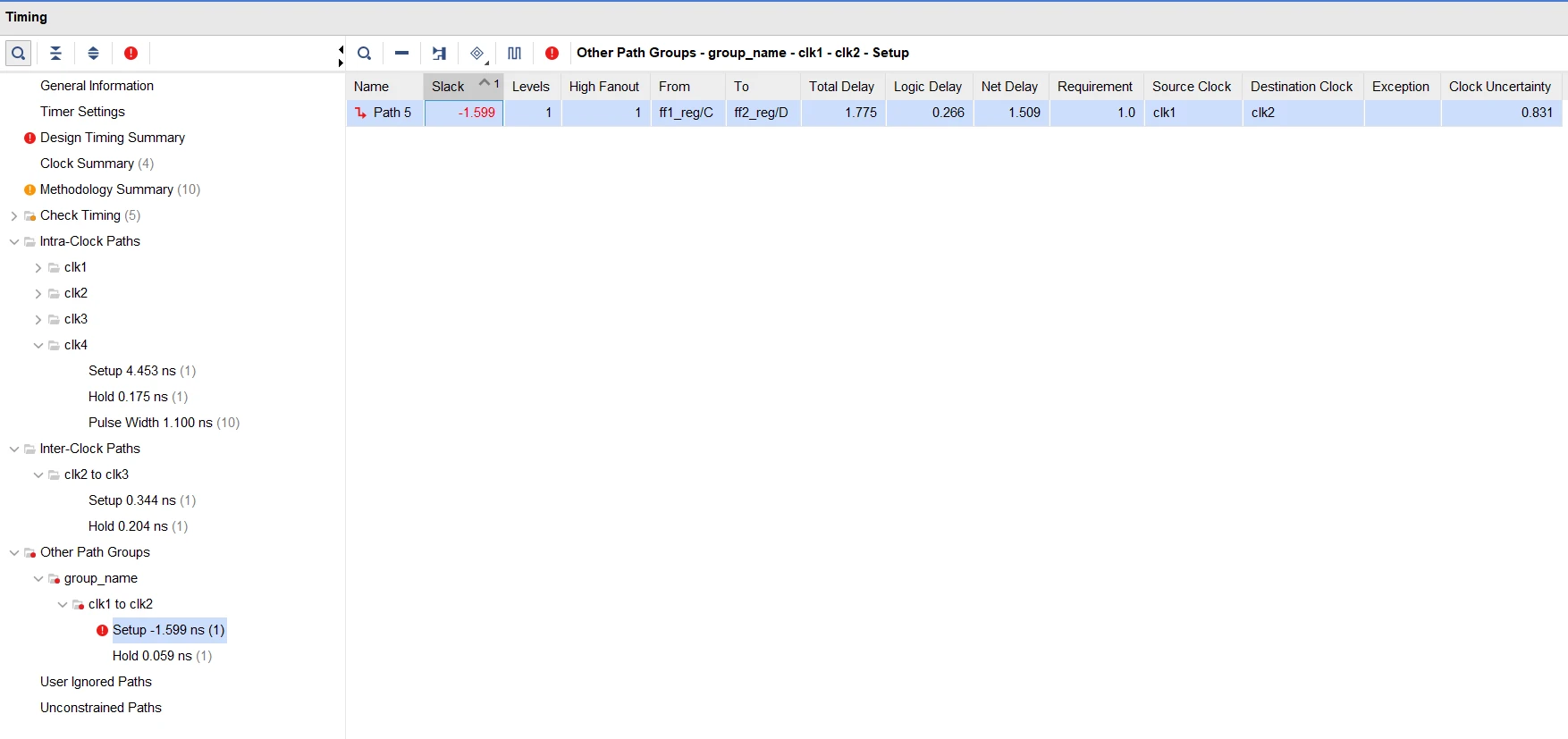

FPGA设计时序约束九、others类约束之Group Path

目录

一、序言

二、Group Path

2.1 基本概念

2.2 设置界面

2.3 命令语法

2.4 命令示例

三、工程示例

四、参考文件 一、序言 在Vivado的时序约束窗口中,存在一类特殊的约束,划分在others目录下,可用于设置忽略或修改默认的时序路径分…

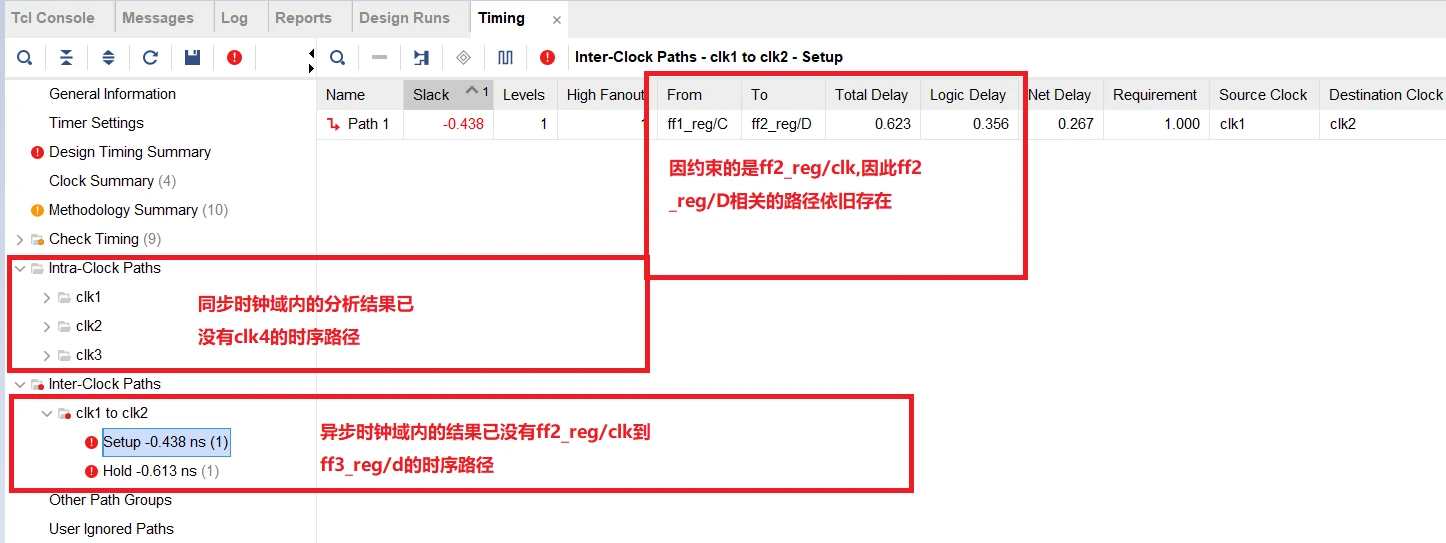

FPGA设计时序约束十、others类约束之Set_Disable_Timing

目录

一、序言

二、Set Disable Timing

2.1 基本概念

2.2 设置界面

2.3 命令语法

2.4 命令示例

三、工程示例

四、参考资料 一、序言 在Vivado的时序约束窗口中,存在一类特殊的约束,划分在others目录下,可用于设置忽略或修改默认的时…

Vivado中增加源文件界面中各选项的解释

文章目录 官方解释结论总结验证增加单个.v文件增加文件夹Copy sources into project 参考文献 本文对Vivado中增加源文件界面Add or Create Design Sources和Add or Create Smulaton sources中的选项Scan and add RTL include files into project、Copy sources into project和…

具于xilinx FPGA的可动态配置DDS频率控制字的DDS IP核使用例程详解

目录 1 概述2 IP examples功能3 IP 使用例程4注意事项5 DDS IP Examples下载位置 1 概述

本文用于讲解xilinx IP 的dds ip examples(动态配置频率)的功能说明,方便使用者快速上手。

2 IP examples功能

本examples 是月隐编写的针对DDS的使…

vivado布线出错opt 31 - 67(opt 31 - 155)

通过右键error用官网得办法还是无法找到报错lut引脚连到了哪里,该引脚property就是unplace得状态(给我得感觉就是悬空了),由于信号在网表文件里面,对我来说它是透明得,因此我只能通过信号名来猜测它得连接状…

【自用】Ubuntu20.4从输入法到ddr200t运行HelloWorld

【自用】Ubuntu20.4新系统从输入法到ddr200t运行HelloWorld 零、编辑bashrc一、搜狗输入法安装二、百度网盘安装三、Vivado2022.2安装四、编译蜂鸟E203自测样例1. 环境准备2. 下载e203_hbirdv2工程文件3. 尝试编译自测案例1. 安装RISC-V GNU工具链2. 编译测试样例 4. 用vivado为…

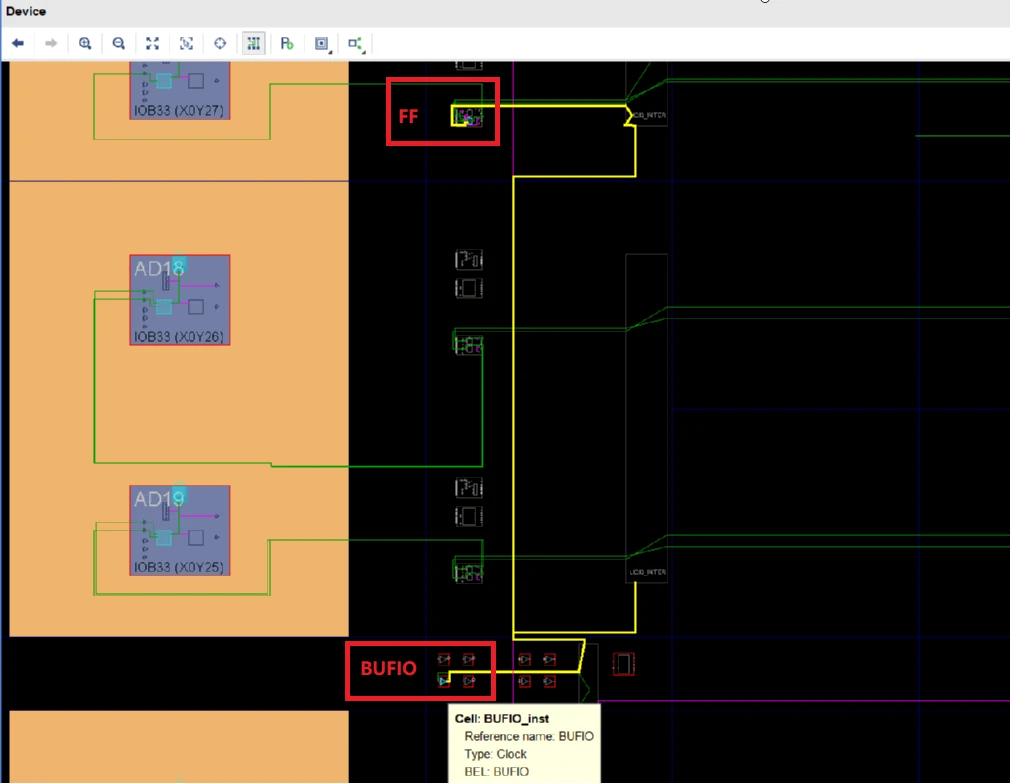

FPGA之时钟规划图解

目录

一、前言

二、时钟规划概念

三、时钟规划的模块

四、时钟规划之时钟单元布局

4.1 BUFG

4.2 BUFH

4.3 BUFR

4.4 BUFIO

五、时钟规划之时钟单元走线

5.1 BUFG->BUFH

5.2 BUFR->FF

5.3 BUFIO->FF 一、前言 对于vivado这类使用verilog语言的进…

Xilinx FPGA平台DDR3设计详解(一):DDR SDRAM系统框架

DDR SDRAM(双倍速率同步动态随机存储器)是一种内存技术,它可以在时钟信号的上升沿和下降沿都传输数据,从而提高数据传输的速率。DDR SDRAM已经发展了多代,包括DDR、DDR2、DDR3、DDR4和DDR5,每一代都有不同的…

C6—Cadence导出的csv转成xdc文件20230902

Vivado工程需要引脚之间的连接才能生成bit流。使用cadence软件设计的原理图可以导出csv文件或者ucf文件,而使用vivado使用以xdc为后缀的文件。使用python读入csv文件,按照一定的格式转换成xdc文件保存,省去了手动添加的步骤。当然需要注意&am…

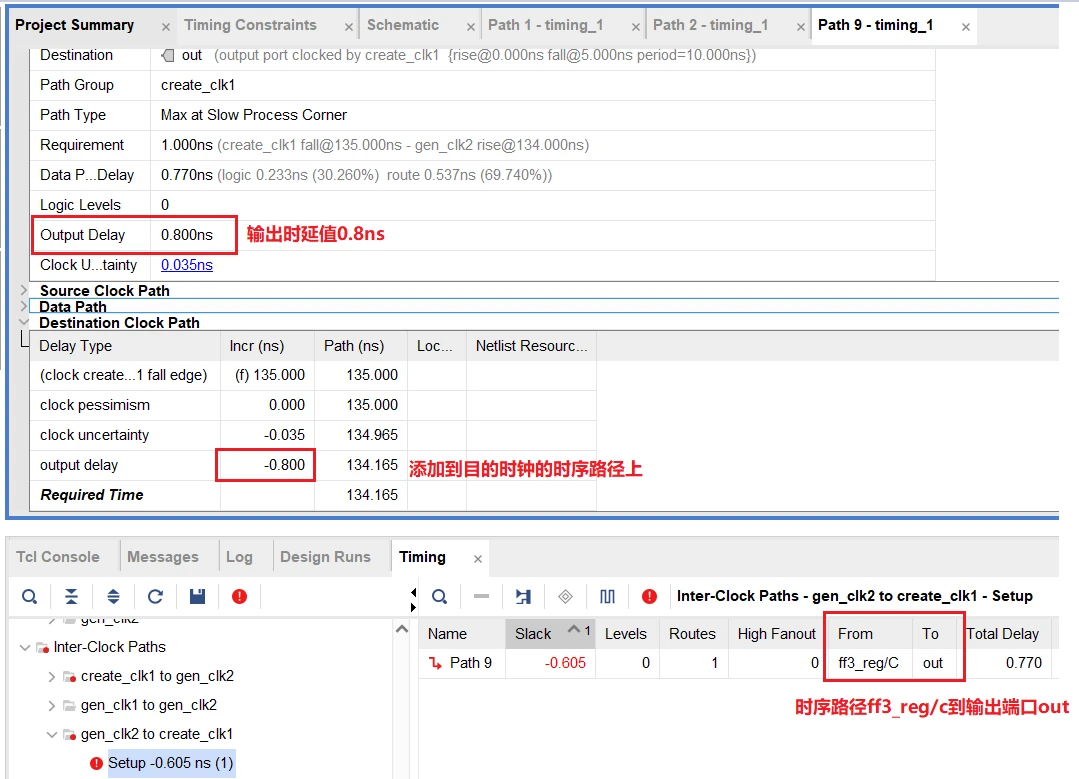

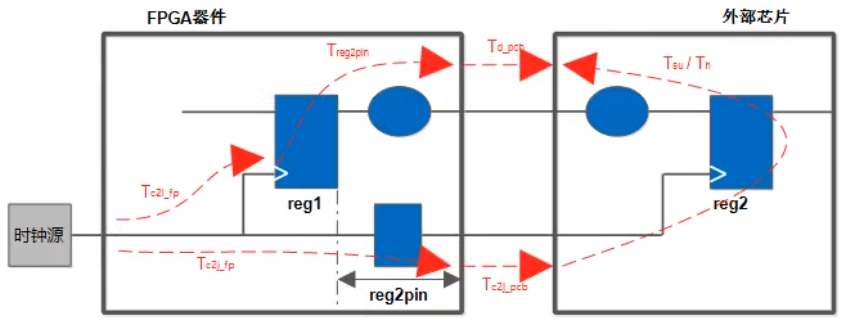

FPGA设计时序约束二、输入延时与输出延时

目录

一、背景

二、set_input_delay

2.1 set_input_delay含义

2.2 set_input_delay参数说明

2.3 使用样例

三、set_output_delay

3.1 set_output_delay含义

3.2 set_output_delay参数说明

3.3 使用样例

四、样例工程

4.1 工程代码

4.2 时序报告

五、参考资料 一、…

FPGA时序约束与分析-简单入门

FPGA时序约束与分析-简单入门 文章目录 FPGA时序约束与分析-简单入门1. 本课程概述2. 时序约束简介2.1 什么是时序约束2.2 合理的时序约束2.3 *基于Vivado的时序约束方法 3. 时序分析的基本概念3.1 时钟与时钟偏差3.2 建立时间和保持时间3.3 时序分析中路径、沿和关系的定义 4.…

HLS 2017.4 导出 RTL 报错:ERROR: [IMPL 213-28] Failed to generate IP.

软件版本:HLS 2017.4

在使用 HLS 导出 RTL 的过程中产生如下错误: 参考 Xilinx 解决方案:https://support.xilinx.com/s/article/76960?languageen_US

问题描述 DESCRIPTION As of January 1st 2022, the export_ip command used by Vivad…

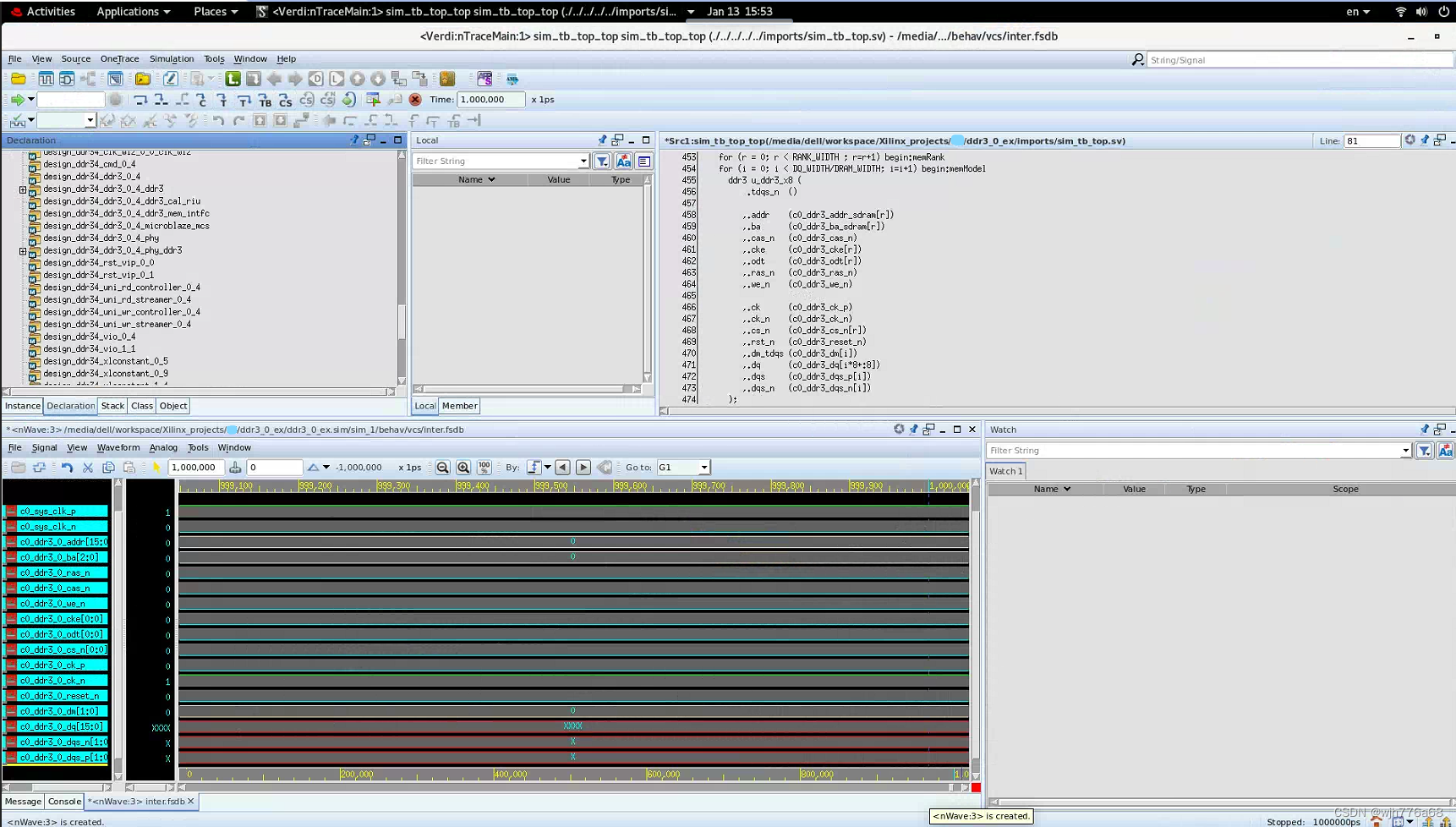

【RHEL】Vivado调用VCS+Verdi联合仿真报错解决

问题描述 在使用VCS Verdi仿真Vivado工程时,点击行为仿真按钮进度条窗口消失后,Verdi窗口并未出现,查看消息报错如下:

vcs: line 34205: 119837 Segmentation fault (core dumped) ${TOOL_HOME}/bin/cfs_ident_exec -f ${X…

vivado 报错之procedural assignment to a non-register result is not permitted“

文章目录 这个错误通常是由于尝试在非寄存器类型的对象上进行过程赋值所引起的。在 Verilog 中,当使用 always 块时,其中的赋值操作应该只用于寄存器类型的变量,比如 reg 类型。非寄存器类型的信号(比如 wire)不能在 a…

vivado切换使用modelsim打不开解决办法

vivado软件切换使用modelsim仿真时,如果出现如下图所示情况 可按下图所示,点击编译Xilinx的仿真库, simulator选modelsim simulator,编译库compiled library location放入新建的文件夹D:\Xilinx\Xlib中,simulator ex…

[FPGA IP系列] 2分钟了解FPGA中的BRAM

FPGA设计中,BRAM是一项非常关键的内置存储资源,FPGA开发需要熟练使用BRAM,今天再复习一下BRAM的知识,包括BRAM的定义、组成、应用等等。

一、BRAM介绍

1、BRAM的定义

RAM是Random Access Memory,也就是随机访问数据…

![Vivado [filemgmt 56-328]生成ip报错解决方法](/images/no-images.jpg)

![vivado报错警告之[Vivado 12-1017] Problems encountered:](https://img-blog.csdnimg.cn/d61ae62d3e93423498dc2b71d2770973.png)

![Modelsim仿真问题解疑二:ERROR: [USF-ModelSim-70]](https://img-blog.csdnimg.cn/img_convert/b31ab1d00592df0a0871369166ec3bf1.png)

![vivado综合出现[Synth 8-91] ambiguous clock in event control](https://pic1.zhimg.com/80/v2-f44adf47707813782381898cd1c54c30_720w.jpg)

![[FPGA IP系列] BRAM IP参数配置与使用示例](https://img-blog.csdnimg.cn/img_convert/bb90386cec9df272311537322199e691.png)

![HLS 2017.4 导出 RTL 报错:ERROR: [IMPL 213-28] Failed to generate IP.](https://img-blog.csdnimg.cn/direct/dd34ed34b085400ca264f79a55f172e7.png)

![[FPGA IP系列] 2分钟了解FPGA中的BRAM](https://img-blog.csdnimg.cn/b4c99a625a2c4f84a061586a235d883d.png)